## EMPLICATION COMPUTING DESIGN

www.embedded-computing.com

**MARCH 2009**

**VOLUME 7 NUMBER 2**

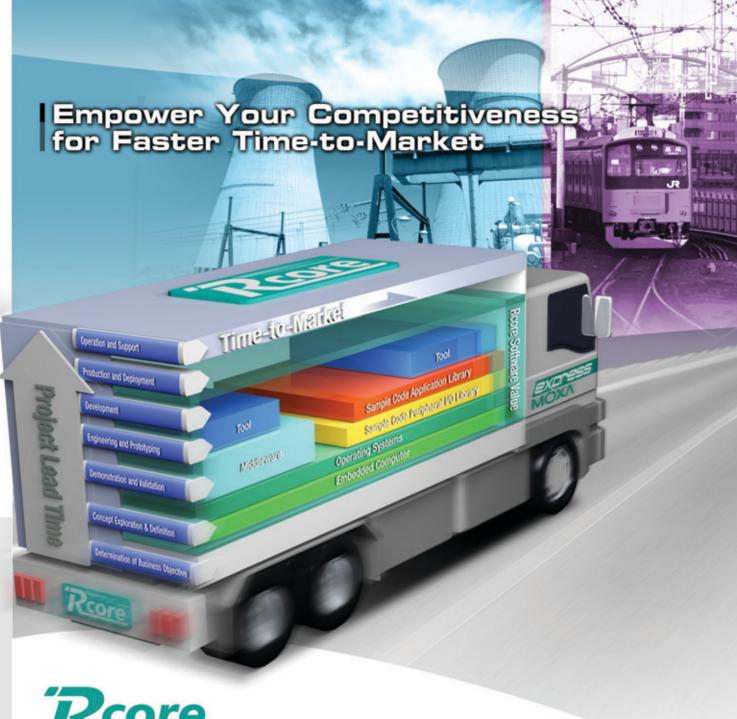

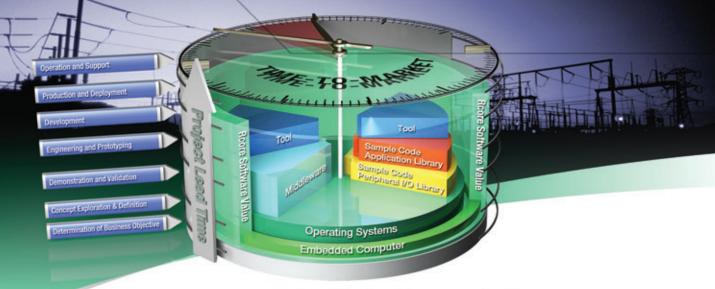

## Integrated platforms: Adding value layer by layer

2009 Components Resource Guide

INCLUDED WITH THIS ISSUE:

MOXA

Ready-to-Run Embedded Software Platform

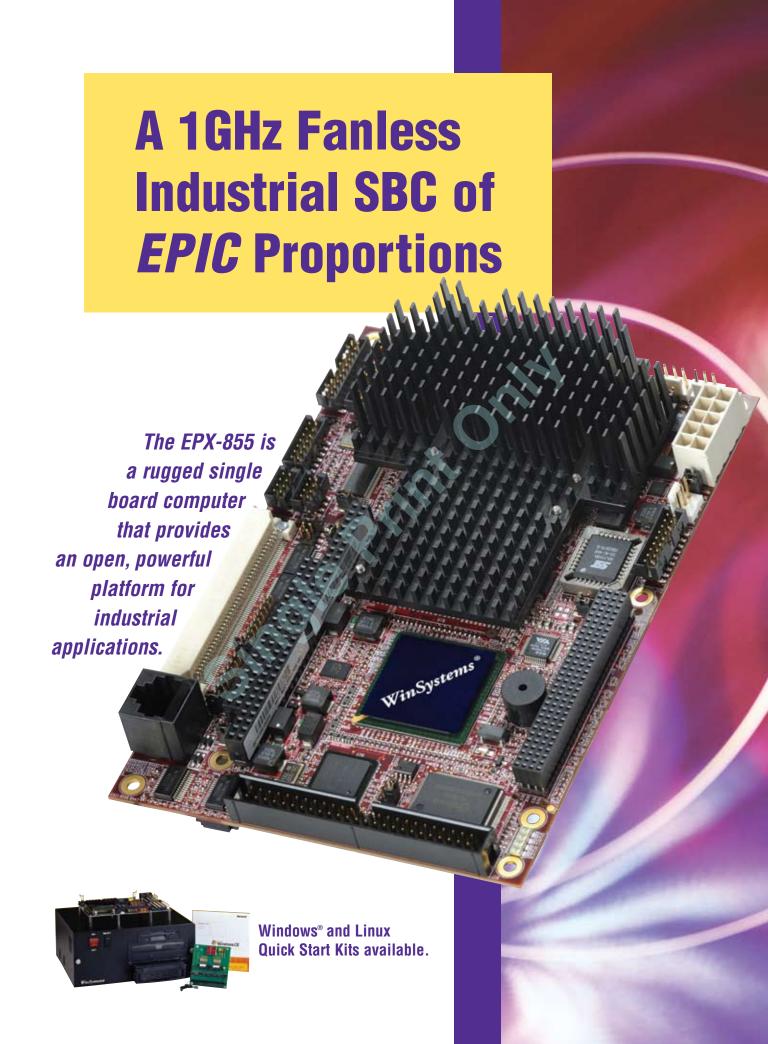

With a wealth of onboard I/O plus expansion options, the EPX-855 supports Linux, Windows® XP embedded, and other x86 real-time operating systems.

- Intel® 1GHz CPU (fanless) or optional 1.8GHz Pentium® M

- Intel® Extreme Graphics 2 technology supports CRT and LVDS flat panels simultaneously with dual independent display and resolutions up to 2048 x 1536

- 802.11 a/b/g wireless support

- Custom splash screen on start up

- Two Ethernet ports; one Gigabit and one 10/100Mbps

- CompactFlash (CF) card supported

- Four serial COM ports, four USB 2.0 ports, 24 bi-directional TTL digital I/O lines, and two UDMA IDE ports

- Bi-directional LPT port, keyboard controller, FDC, and AC97 audio

- PC/104 and PC/104-Plus Bus expansion

- EPIC sized 4.5" x 6.5" and RoHS compliant

- +5V only operation

- -40°C to +70°C operational temperature range

- Responsive and knowledgeable technical support

- Long-term product availability

- Quick Start Kits offered for easy software development

Contact us for additional information or OEM pricing. Our helpful and knowledgeable factory application engineers look forward to working with you.

Call 817-274-7553 or Visit www.winsystems.com/EPX-855 Ask about our 30-day product evaluation

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

Volume 7 • Number 2

www.embedded-computing.com

#### Columns

#### 8 Editor's Foreword

Is now the time to invest in tools?

By Jerry Gipper

#### 10 Technology Passport

Look Ma, no driver

By Hermann Strass

#### 12 Consortia Connection

Smart standards for wireless technologies

14 Ingenuity @ work

Simplified HMI development

#### **Departments**

#### 52 Editor's Choice Products

By Jerry Gipper

#### Resource Guide

Design aids 34

Interfaces 35

Microcontrollers and processors 36

Power management 39

Programmable logic 40

Software 47

#### Cover/Web Resources/Events

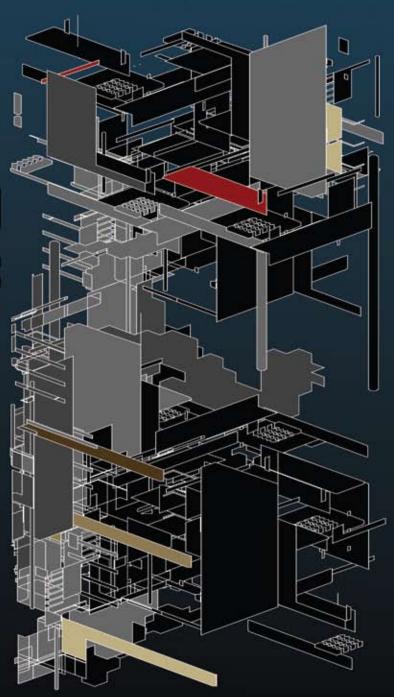

#### On the cover

Platform-Oriented Architectures (POAs) can be packaged in layers, making systems integration easier. Check out the Special Feature starting on page 16 for more information on how POAs can help resolve design challenges.

#### E-casts

Register at: www.embedded-computing.com/ecast

What makes a Real-Time OS indispensable? March 12. 11 a.m. EDT

Embedded multicore system development fundamentals March 12, 2 p.m. EDT

#### E-letter

www.embedded-computing.com/eletter

PCle Gen 2: Not just more bandwidth By Touseef Bhatti, PLX Technology

#### **Web Resources**

#### Subscribe to the magazine or E-letter at:

www.opensystemsmedia.com/subscriptions

#### Read industry news at:

www.embedded-computing.com/news

#### Submit news releases, new products, white papers, and videos at:

submit.opensystemsmedia.com

#### **Events**

#### **Multicore Expo**

March 16-19 • Santa Clara, CA www.multicore-expo.com

#### **Embedded Systems Conference Silicon Valley**

March 30-April 3 • San Jose, CA http://esc-sv09.techinsightsevents.com

#### **Features**

#### **Special Feature**

16 What's in your platform?

By Jerry Gipper

#### Chip and board debugging

22 Protocol analyzers simplify USB debugging

By Etai Bruhis, Total Phase

#### Core IP licensing

26 Software Bill of Materials improves Intellectual Property management

By Mahshad Koohgoli, PhD, and Sorin Cohn-Sfetcu, PhD, Protecode

#### Programmable logic

28 The high price of low-cost FPGA development boards

By Rob Evans, Altium Limited

#### Software

32 Trends are good for press, not necessarily for sockets

By Jean J. Labrosse, Micrium

2009 OpenSystems Media ® © 2009 Embedded Computing Design All registered brands and trademarks in *Embedded Computing Design* are property of their respective owners.

## Annapolis Micro Systems The FPGA Systems Performance Leader

## WILDSTAR 5 for IBM Blade The Perfect Blend of Processors and FPGAs

Fully Integrated into IBM Blade Management System

Abundant Power and Cooling Ensure Maximum Performance

Made in the USA

#### **Ultimate Modularity**

From 2 to 8 Virtex 5 FPGA/Memory Modules Input / Output Modules Include: Quad 130 MSps thru Quad 500 MSps A/D 1.5 GSps thru 2.2 GSps, Quad 600 MSps A/D Dual 1.5 GSps thru 4.0 GSps D/A Infiniband, 10 G Ethernet, FC4, SFPDP

Direct Seamless Connections with no Data Reduction

Between External Sensors and FPGAs

Between FPGAs and Processors over IB or 10GE Backplane

Between FPGAs and Standard Output Modules

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com (410) 841-2514 www.annapmicro.com

for your embedded critical network application

#### COMETH

More than 30 models... cPCI, VME, V

#### ComEth 4300a

- 4 front Giga ports (copper or fiber

- 2 front 10 Gig ports

- 20 rear Gigabit Ethernet ports

- Compliant with PICMG2.16

- 12 front ports (copper and/or fiber)

- 9 rear Gigabit Ethernet ports

- Compliant with PICMG2.16 / VITA31.1

- Full managed L2/L3 switch

- up to 128 GBytes of Nand flash

- · for applications in harsh environments

For more information on our products and services... www.interfaceconcept.com +33 (0)298 573 030

#### Embedded COMPUTING DESIGN

#### Embedded COMPUTING

DSP-FPGA.com

#### **Military**

PC/104 form factors

#### **Embedded and Test & Analysis Group**

Jerry Gipper, Editorial Director jgipper@opensystemsmedia.com

Don Dingee, Contributing Editor

Jennifer Hesse, Senior Associate Editor jhesse@opensystemsmedia.com

Hermann Strass, European Representative hstrass@opensystemsmedia.com

David Diomede, Art Director

Steph Sweet, Creative Director

Konrad Witte, Senior Web Developer

Joann Toth, Senior Designer

Monique DeVoe, Copy Editor

Phyllis Thompson

Circulation/Office Manager subscriptions@opensystemsmedia.com

#### Sales Group

Dennis Doyle, Senior Account Manager ddoyle@opensystemsmedia.com

Tom Varcie, Senior Account Manager tvarcie@opensystemsmedia.com

Doug Cordier, Account Manager dcordier@opensystemsmedia.com

#### Andrea Stabile

Advertising/Marketing Coordinator astabile@opensystemsmedia.com

Christine Long, Digital Content Manager clong@opensystemsmedia.com

#### **International Sales**

Dan Aronovic, Account Manager - Israel daronovic@opensystemsmedia.com

Sam Fan, Account Manager - Asia sfan@opensystemsmedia.com

#### **Regional Sales Managers**

Ernest Godsey, Central and Mountain States egodsey@opensystemsmedia.com

Barbara Quinlan, Midwest/Southwest bquinlan@opensystemsmedia.com

Denis Seger, Southern California dseger@opensystemsmedia.com

Sydele Starr, Northern California sstarr@opensystemsmedia.com

Ron Taylor, East Coast/Mid Atlantic rtaylor@opensystemsmedia.com

#### **Reprints and PDFs**

Nan Lamade 800-259-0470

license@opensystemsmedia.com

#### **Editorial/Business Office**

16626 E. Avenue of the Fountains, Ste. 203 Fountain Hills, AZ 85268 Tel: 480-967-5581 ■ Fax: 480-837-6466

Website: www.opensystemsmedia.com

Publishers: John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial: Rosemary Kristoff

Vice President Marketing & Sales:

Patrick Hopper

phopper@opensystemsmedia.com

Business Manager: Karen Layman

ISSN: Print 1542-6408, Online 1542-6459

Embedded Computing Design is published 8 times a year by OpenSystems Media LLC, 16626 E. Avenue of the Fountains, Ste. 203, Fountain Hills, AZ 85268.

Subscriptions are free to persons interested in the design or promotion of embedded computing systems. For others inside the US and Canada, subscriptions are \$56/year. For 1st class delivery outside the US and Canada, subscriptions are \$80/year (advance payment in US funds required).

Canada: Publication agreement number 40048627 Return address: WDS, Station A, PO Box 54, Windsor, ON N9A 615

POSTMASTER: Send address changes to *Embedded Computing Design*, 16626 E. Avenue of the Fountains, Ste. 203. Fountain Hills. AZ 85268

ne of the most important decisions a medical OEM makes is their choice of an embedded computer. It's at the heart of any system. At VersaLogic, we design our embedded computer products to ensure high reliability and long-term availability. That's why our single board computers can be found in a long list of medical products. And because we understand that medical customers have special requirements, every board we make is run through exhaustive quality tests, ensuring that we deliver only the best.

Whether you need one of our standard products or a version customized to your needs, our skilled technical

Contact us to find out how for more than 30 years we've been perfecting the fine art of extraordinary support and on-time delivery: One customer at a time.

staff will work with you to meet your exact specifications.

### Editor's Foreword

Jerry Gipper

## Is now the time to invest in tools?

Determining when you should invest in development tools is often a hard decision to make, especially during an economic recession. Yet it is still a decision that needs to be made.

During boom times, the push to get more done is commonly addressed by throwing more human resources at a design task, with managers asking for more engineers to keep projects on schedule. Investments in development tools and new processes take a backseat. These investments meet resistance because design teams don't have the luxury of taking time to investigate toolset options or to learn a new tool suite and processes. They are focused on getting the project out the door on time.

During economic declines, resources are stretched as companies make cutbacks in staff and spending. Getting sign-off on new development tools is not likely to get any attention while projects fall behind.

Several studies illustrate the benefits of using advanced development tools such as simulators, Model-Driven Development (MDD) tools, and other electronic design automation tools. How much time and money can be saved varies, but most reports

reach the conclusion that definite savings can be achieved. A December 2008 report titled "The Economics of Embedded Development, Testing, Deployment, and Support" by Embedded Market Forecasters (www.embeddedforecast.com) presents an example that shows how companies can attain project improvement approaching 30 percent. There is no question that good, solid development tools can reduce development cycle times, shorten time to market, and improve the quality of your product.

Selecting the right solutions is another story. Development tools come in all types, from simple and basic to very complex and robust. You must clearly understand each tool and how it will work in your design environment. The often inexpensive entrylevel tools might not have the right sets of features. For instance, a low-end MDD tool might not provide validation or traceability

to your requirements, reduce programming errors or test time, or improve the quality of the final product as expected.

On the other hand, deluxe tools can be overkill, with features that are not necessary for your development environment or that are so complicated that they are difficult to learn or use.

Don't let price be the sole driver. Sometimes the best tools are inexpensive; other times, "you get what you pay for" applies. You should employ an in-house specialist who tracks development tools, someone you can turn to when a decision needs to be made. A readily available expert who fully understands the pros and cons of a tool and can interpret its impact on your orga-

nization and projects is hard to come by. Relying on marketing hype and sales pressure can lead you astray.

My belief is that now is the right time to consider investments in upgrading your development tools. You will want to be in a position to recover from this downturn quickly, riding the upslope that will likely occur in the coming months.

With the right investment, you could save 25-30 percent on your next project,

reduce time to market, meet schedule commitments, and produce better design results.

As you eventually start restaffing, look for engineers who are competent and skilled in using these new tools. Underemployed engineers should take advantage of this time to learn new tools, making them more marketable assets to the companies that will emerge out of this recession.

Feel free to share your comments through e-mail or visit our blog at www.embedded-computing.com to add your comments.

Jerry Gipper Editorial Director jgipper@opensystemsmedia.com

Don't let price be the sole

driver. Sometimes the best

tools are inexpensive; other

times, "you get what you

pay for applies.

### VECTOR

**Short Lead Times**

**Custom Configurations**

**Factory Support**

## Hermann Strass

### Technology Passport

#### Look Ma, no driver

#### **Automated system secures subway**

The city of Nuernberg is a pioneer in industrial technologies. In 1835, the first scheduled train service in Germany traveled between Nuernberg and the neighboring city of Fuerth. Last June Nuernberg launched the U3 line, Germany's first subway line to use driverless trains as well as the world's first underground metro to run both automated and conventionally operated trains over the same tracks. Figure 1, courtesy of Siemens, shows the U3 line on opening day.

Other driverless subway systems, such as the automated people mover at the airport in Atlanta, Georgia, control access using platform doors aligned with train car doors that always open on the same side in each direction of travel. In the Nuernberg system, cars are coupled and trains are switched automatically. Every inch of the railway track is monitored to detect objects.

Transit authorities typically equip automated subways with doors that block the dangerous area at the edge of the platform until the train stops. This wasn't possible in the U3 line because of its mixed automatic/manual operation and curved platforms.

To ensure safety, the U3 system uses video monitoring and a dense grid of sensing beams over the tracks near the platform edge. If a person or object falls onto the track or between cars, the system immediately halts all trains in the area. Solid sills extend from doors when a train is stopped to prevent objects from getting caught in the gap between the train and the platform. Sensors in the rubber edges of the doors register even the slightest pressure. The hem of a coat stuck in the door is all it takes to keep the train from leaving the station.

The control center monitors the train car interior via video cameras. Passengers who activate an alarm are automatically connected with the control center through digital voice radio. The automated system does not require traditional mechanical or electrical signals along the tracks.

#### **Embedded computers steer trains**

An Automatic Train Control (ATC) system from Siemens controls the U3 trains' movements and operates the signal boxes. These trains contain onboard embedded computers that continually exchange data with the higher-level control system. Data

Figure 1 I The U3 line in Nuernberg uses driverless trains.

includes the destination and speed of each train, track switching information, and the side of the train that will face the platform at the next station. While one onboard computer uses data from the ATC to control the driving process, a second computer monitors the actions of the first and makes corrections if necessary.

The ATC system can monitor and control train movements autonomously. All control systems are connected in a triple redundant voting configuration, meaning that all trains are allowed to run as long as two computers provide identical results. If not, the system immediately halts the trains and central control takes over operations. Objects blocking the doors have presented the greatest problem thus far.

The U3 trains travel at an optimal speed in accordance with the timetable and distance between stations. Other benefits of the driverless system include shorter train intervals of 100 seconds instead of 200 seconds and the ability to quickly dispatch additional trains for major events. The centralized automated subway is more energy-efficient and safer than driver-operated systems.

The Georg Simon Ohm University of Applied Sciences in Nuernberg is working on a decentralized system for driverless subway operation. Other driverless subway lines are currently under construction in Barcelona, Spain; Uijeongbu, Korea; and other cities around the globe.

## Our Advanced Managed Platforms™ will take you there!

Design challenges today are more acute than they were just a year ago. At Performance Technologies, we understand these challenges. Our Advanced Managed Platforms™ provide flexible and scalable solutions for MicroTCA™ and CompactPCI®. These pre-integrated hardware and software platforms enable you to reduce development costs and improve time-to-market while advancing your product design initiatives.

We are the <u>only</u> company that can offer you <u>both</u> pre-integrated embedded hardware and a CGL Registered 4.0 Linux<sup>®</sup>, with our NexusWare<sup>®</sup> suite of software.

So the next time you need a ready-to-develop solution, call Performance Technologies and discover how our Advanced Managed Platforms™ can meet your design challenges.

Flexible MicroTCA™ Platforms

Carrier Grade Linux® NexusWare® OS

Scalable CompactPCI® Platforms

Phone: 585.256.0200 + www.pt.com + E-

E-mail: info-request@pt.com

## Consortia **Connection** for wireless

## Smart standards technologies

#### **IPSO Alliance**

www.ipso-alliance.org

The IP for Smart Objects (IPSO) Alliance promotes the concept that Internet Protocol (IP) is the networking technology best suited for connecting sensor-equipped devices - referred to as smart objects - and delivering information gathered by those objects. Smart objects transmit information about their condition or environment (for example, temperature, light, motion, and health status) to locations where that information can be analyzed, correlated with other data, and acted upon. These

objects are used in automated homes and offices, factory automation, asset tracking, patient monitoring, industrial **Alliance** and safety systems, and many other applications.

"More and more utilities and OEMs are viewing embedded IP as the long-term solution and proprietary approaches and ad hoc alliances as merely an interim step," states Geoff Mulligan, IPSO Alliance chairman. "They are recognizing that only IP can support a wide variety of networking technologies with the needed scalability and interoperability that organizations require."

The IPSO Alliance is planning three large-scale interoperability test events in 2009, the first of which will test endto-end IP-based interoperability across the Internet by employing the nextgeneration IPv6 protocol over local and wide area communication media. The event will demonstrate open standardsbased sensor networking solutions that deliver the global scalability, security, performance, and flexibility needed for future applications.

Other events later in the year will include demonstrations of multivendor devices communicating within a sensor network using the Internet Engineering Task Force 6LoWPAN (RFC 4944) standard for IPv6 over low-power wireless personal area networks. Each subsequent test will increase the scope of vendors and the diversity of interoperating media types including IEEE 802.15.4, Wi-Fi, Ethernet, and WiMAX.

www.zigbee.org

The ZigBee Alliance, a global ecosystem of companies creating wireless technologies for use in energy management, commercial, and consumer applications, finished 2008 with more than 300 members. Utilities across the United States and Canada have validated ZigBee Smart Energy as the leading wireless standard for implementing home area networks in conjunction with Smart Grid initiatives.

"When you consider that already more than 25 million homes in North America will be outfitted with a smart meter equipped with ZigBee with more on the way, the opportunities for our members to provide consumers with more control of their lives are incredible," asserts Bob Heile, chairman of the ZigBee Alliance. "Consumers will remotely control their homes and manage their energy use thanks to ZigBee Smart Energy's inherent Internet connectivity."

The ZigBee Smart Energy profile was ratified in May 2008 and made publicly available in June. Utilities and consumers can select from 20 ZigBee Smart Energy Certified products representing a range of devices for managing home energy consumption including electricity meters, thermostats, and in-home displays.

In February the ZigBee Alliance and the HomePlug Powerline Alliance announced that they are joining forces with the Electric Power Research Institute to develop a standard communication approach for home area networks to use advanced metering infrastructure. The initiative will provide the flexibility for utilities to integrate ZigBee and HomePlug devices when implementing smart metering programs as well as expedite the rollout of energy management and efficiency programs to consumers.

For land-based or airborne applications, the military needs COTS embedded sub-systems that deliver the optimum combination of performance, reliability, cost and rapid time-to-market. And Aitech has delivered just that since 1983!

We're still in front... Aitech got a big jump on everyone way back when...and we've kept well ahead of the pack in developing advanced embedded sub-systems based on leading edge commercial technologies adapted to harsh environment applications.

We don't compete with you... A lot of board level companies claim to be systems integrators. We don't. We leave the systems integration to the companies that do it best: our customers...companies just like yours!

We have what it takes... Our VME and CompactPCI SBCs, PMCs, memory, I/O, graphics and chassis are in a class by themselves. And they're backed by world class software and technical support, program and lifecycle management, testing and more.

We've been there... Aitech sub-systems are in widespread use in the world's most demanding military/aerospace applications: from radar, missile and weapons control to mission-critical data voice sub-systems...from mission computers and display consoles to ECM, sight head stabilization and counter measure control...from power control and conditioning to advanced imaging systems. And that's just for starters.

Don't take our word for it... Compare Aitech's offerings and expertise to any company in the COTS embedded marketplace. Land or air. Or for that matter, sea or space. Come to talk to us.

Aitech Defense Systems, Inc. 19756 Prairie Street Chatsworth, CA 91311 email: sales@rugged.com Toll Free: 888-Aitech8 - (888) 248-3248 Fax: (818) 718-9787

### Simplified HMI development

sroblen.

Designing Human-Machine Interfaces (HMIs) is becoming a significant challenge for designers. Embedded devices are shrinking in size, making it difficult to develop useful and intuitive HMIs with the right combinations of features in a short time-to-market window.

solution

Software tools can help manufacturers build user interfaces at a high level using programs like Photoshop for graphics and Visio for screen flow. Developers can then integrate those pieces of technology into actual code that can run on the device itself.

#### Converting creativity into code

This decade has seen dramatic improvements in display technology, generating an explosion of uses for graphics displays in desktop, workstation, and embedded systems. From in-car navigation systems, mobile phones, and portable MP3 players to airports and power plants, flat-panel displays are showing up everywhere. Consequently, the HMI has emerged as a critical product differentiator that provides a window into an array of powerful product features.

Although display technology has improved dramatically, HMI software development has lagged behind, producing many abysmal user interfaces. This delay can be attributed to today's complex, programmer-centric HMI tools, which discourage the participation of the graphic artists, industrial designers, and application experts needed to develop effective user interfaces. Furthermore, because today's devices come with custom processors and/ or Operating Systems (OSs), building user interfaces requires special skills and knowledge.

To aid designers in this difficult task, Altia provides cohesive, easy-to-use HMI development tools that wrap high-level modeling and graphical tools around detailed

Altia, Inc. Founded: 1991

Management: Michael Juran, CEO Headquarters: Colorado Springs, CO

URL: www.altia.com

custom programming. The tools hide the processor from developers so they can focus on their applications. A code generator produces code for the chosen processor architecture, and everything from graphics to logic gets used and reused.

Altia helps bridge the gap between the widely dissimilar needs of the creative process and the programming process. The company's tools assist artists by providing a WYSIWYG graphics and HMI editor that allows them to draw and import graphics from their favorite graphics design tools. The software likewise aids programmers by providing code generators, language translators, APIs, and OS-specific graphics libraries that convert the artist's HMI design into deployable code that can be integrated with the programmer's application code and run on a variety of OSs and hardware.

## Create Your Own PMCs Custom I/O as Easy as 1, 2, 3!

The Technobox *Micro Mezzanine System*™ is based on a simple idea – provide embedded systems designers with a foundation for innovation and flexibility. Provide a highly-granular, modular architecture featuring a range of configurable FPGA-based carrier boards and an extensive variety of micro mezzanine Electrical Conversion Modules (ECMs) that can be assembled in thousands of combinations. Provide an environment in which a designer can create an array of unique, *future-proofed*, board-level solutions. But without the costs normally associated with custom board development and manufacture, while speeding development and reducing time to market. It's the logical next step in mezzanine systems.

Select an FPGA-based Carrier

Choose I/O Conversion Modules Assemble with IP Core and ECM Code

**Patent Pending**

- · Build Your Own Board by Mixing and Matching Modular Components

- · Thousands of Possible Combinations

- · Flexible, FPGA-based, Patent-pending Architecture

- Incorporate Multiple Functions on a Single Board

- Design and Build Application-specific, Future-proofed Solutions

- Accelerate System Development, Reduce Time to Market

To learn more about the Technobox Micro Mezzanine System, visit: www.technobox.com/mmsintro-fp.htm

#### What's in your platform?

By Jerry Gipper

Designing embedded computer systems is always difficult. Innovative technologies with increasing performance levels and smaller packaging present new obstacles every day. Fortunately, suppliers are making design easier by promoting the concept of a Platform-Oriented Architecture (POA), which provides a way to move up the supply chain and make the design and integration efforts go more smoothly. Just as politicians use their platforms to kick-start their programs, POAs provide a launching pad for embedded devices. So the question is, what should you know about platforms before starting your next project?

"In today's challenging business environment, developers are looking for ways to reduce cost through extensive software reuse and by leveraging turnkey platforms that combine best-of-breed hardware and software." – Tony Massimini, chief of technology, Semico Research Corporation

#### **POA** defined

The definition of Platform-Oriented Architecture varies slightly from software to chips to boards to systems, but the concept remains the same. It is a bounded and integrated suite of components consisting of either or both software and hardware optimized to enable further integration into a final product for a specific application. Advanced platforms combine hardware and associated software designed to serve as the basis for a number of different systems to be integrated. Many other devices – Systems-on-Chip (SoCs), Application-Specific Standard Products (ASSPs), SBCs, and systems in a variety of combinations – are now considered platforms.

"The ultimate Platform-Oriented Architecture is an FPGA because you can do anything with it," asserts Craig Rawlings, senior director of product management at Certicom. "The idea of doing something universal is a pipe dream. But if we bind the problem, then it makes a lot of sense, and you can scope things in a way that streamlines a number of options, plus save on R&D and manufacturing."

#### How platforms evolved

In the early days of electronics, devices were usually custom-designed for a

specific objective. Hardware and software were designed from scratch and took forever to develop. As the market matured, suppliers started to anticipate the needs of developers, but they did so in haphazard ways. They tried to maximize their market coverage and design products that served as many users as possible. Generalpurpose processors, computer boards, and Real-Time Operating Systems (RTOSs) emerged. Developers had to force-fit or tweak components to meet their specific application requirements.

From Rawlings' perspective, the first POA was really a CPU because it was programmable; you could do anything with it. But microcontrollers were among the first to formally embrace the platform concept. Suppliers would package together the core processor with various configurations of memory and I/O to target specific controller applications such as industrial control or medical devices.

Rawlings speculates that system architects stepped in and said, "Let's not build an architecture that tries to be everything to everybody." They proposed building a platform for a PDA or a mobile telephone – something more specific with binded features that are known requirements. Instead of building three chips or boards, designers could build one chip or board with selectable modes that can be turned off and on.

Eventually, suppliers started making alliances with others in the market to provide more complete solutions for embedded systems developers. Early attempts were loose alliances or ecosystems that covered as many of the design bases as possible. This made it easier for developers to get all the right pieces in place, but it still was a long road to product completion. Designers had to contact and work with multiple sources, lacking the assurance that pieces were fully compatible or even available.

These alliances and ecosystems evolved over time. In many cases, the technologies were combined in packages that made the development path smoother and more efficient. Suppliers started talking about moving up the supply chain by offering more complete and integrated solutions. This strategy became even more effective as the electronic hardware and software suppliers began addressing specific application segments. Various hardware and

Figure 1 I Like matryoshka dolls, POAs can be nested in different layers, with additional features and value incorporated at each layer.

software components were integrated, and the platform concept stuck.

In time, the PC emerged as a dominant general-purpose platform. However, many embedded applications cannot use a PC platform because they have size, weight, and power restrictions that make it impractical to use a PC. This issue led to the development of platforms that address the specific needs of embedded applications. Functions specific to market applications, from mobile devices to communications infrastructure, were defined and developed.

#### **Platform components**

In many ways, POAs are like matryoshka dolls in that they can be nested beginning at the IP layer and moving through to the packaged system level (see illustration in Figure 1). Additional features and value are incorporated at each layer as integration becomes more complex. IP is packaged into a platform that can make integration into a chipset easier; chipsets are packaged into devices that make board design easier; boards are packaged into platforms that make systems integration easier; and systems are packaged in ways that make adding the final layers of value easier.

#### Chips, boards, and systems

Hardware platforms include the processing element, memory, and user I/O appropriate to certain applications. SoCs are usually targeted at specific applications, making them entry-level platforms by definition. ASSPs are designed for very targeted applications and thus are considered platforms. Add some specific software to support the hardware, and you get an even more robust and complete platform. Semiconductor suppliers often go the next step and develop reference designs that include not only the processor, but also a fabricated board and software package that speeds the use of the product in a final design.

Platforms were mentioned prominently in Xilinx's recent launch of its Spartan-6 and Virtex-6 products. "We are reaching the tipping point at which FPGAs become the prevailing silicon platform of choice for electronics manufacturers

#### swissbit<sup>®</sup>

#### **Experience the Value**

### Industrial SDHC Card S-210 Series

- Fully SDHC Compliant

- SD & SPI Mode Supported

- Data Loss / Power Failure Protection

- Enhanced ESD Protection 15kV

- High Reliability Design & Construction

- Industrial & Extended Temperature Grades

quality manufacturer of DRAM & Flash Memory Products

swissbit.com

#### Special Feature: Platform-Oriented Architecture

who need customization to differentiate their products but are faced with incredibly unattractive ASIC development costs," remarks Moshe Gavrielov, Xilinx president and CEO. "But in order for customers to increase their adoption of FPGAs, it's essential that we provide a comprehensive design environment that enables global design teams to address the 'programmable imperative' and deliver products faster under these challenging economic and business conditions."

The Xilinx targeted design platform strategy encompasses the integration of five key elements:

- New Xilinx Virtex-6 and Spartan-6 FPGAs

- Design environments supporting and integrating industry-proven methodologies

- Scalable boards and kits adopting the industry-standard FPGA mezzanine connector

- **>** Socketable IP cores

- **>** Robust reference designs

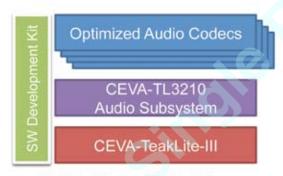

These elements were emphasized as important features in another recent product debut. The CEVA HD-Audio solution is supported by a Software Development Kit (SDK) that includes software development tools, development boards, software system drivers, and an RTOS to enable quick and easy system development and integration. The CEVA-HD-Audio is further complemented by extensive algorithms and applications from a third-party development community.

#### **OSs**

OS platforms consist of an integrated suite of modules: the OS, firmware, and device drivers to run the target device's peripherals, file system, libraries, communications protocols for connectivity, and user application. OS suppliers have expanded the integration layer of additional software into their core OSs to incorporate much of the software that makes it easier to focus on the final application. They have continually improved the API, eliminating the need to worry about the routine middleware needed within an industry.

#### Tools

The platform strategy also applies to development tools. Greg Sykes, director of architecture and modeling at IBM Rational, points out that tools benefit from being packaged into platforms specific to certain market segments. Many companies such as cell phone and automotive manufacturers have their own methods for program management and development. Crafting platforms that conform to a familiar look and feel and providing tools that let designers quickly create modules needed by the application can save significant time in the lab.

#### The benefits of using a platform

Platforms resolve the problems involved in hardware and software component selection and ease the challenges of integrating and debugging the design, not to mention reduce the hassle of tracking down all the various components needed to develop a complete product. Today, suppliers tend to specialize in facets of the hardware or software needed for an embedded computer system. Because of this specialization, it can be very difficult

to chase down remaining components for the final design.

Other suppliers have eased this challenge by integrating the specialized components into a platform. The level of integration can range from simply providing a reference, in which case it probably is not a true platform solution, to a fully integrated and tested configuration. The more integrated the platform, the higher the quality and reliability of the final product, if all goes to plan.

According to Wind River, development tools that are designed and tested with a platform strategy in mind can provide developers with visibility into the entire platform: application code, third-party libraries, and the OS. Developers can monitor variables, optimize performance, and find memory problems – all while the system is still running.

"Increasing competition coupled with challenging economic conditions place further demands on organizations to implement innovative services that reduce costs and streamline operations," states Greg Buzek, president of IHL Group. "By allowing plug-and-play connectivity with peripherals, embedded OSs such as Windows Embedded POSReady 2009 provide the flexibility in system components and software that retailers need, allowing them to lower the cost of ownership and increase efficiencies at the front end."

Targeted POAs help enable software and hardware designers alike to leverage open standards, common design methodologies, development tools, and runtime platforms. This allows designers to spend less time developing application infrastructure and more time building differentiating features into the end application.

#### Integration

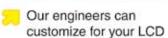

Integration drives many of the other benefits of a platform, making it easier to add and replace components with some level of plug-and-play support. "We do the work of integrating all of this stuff together and making it work for a specific architecture," remarks Dan Cauchy, director of marketing at MontaVista.

"In some cases, we write a lot of this stuff ourselves – for example, the porting of the Mozilla browser to ARM."

Cauchy mentions that getting integration to work at a high-quality level requires many staff-years of work. "Device manufacturers are telling us that this is really valuable because they get to start with an entire solution, and on top of that, it is fully supported by MontaVista," he says.

#### Features and common interfaces

Targeted POAs have the right set of features and interfaces for the target application. The choices have been well thought out and vetted through the target industry. Suppliers need to know their customers' markets to make the right choices.

OS platforms provide a common API, minimizing or even eliminating the need to agonize over hardware. Programmers can write a more generic interface and not worry about the details of the device. On the hardware side, interfaces like Ethernet, USB, CAN, and other application-specific choices are supplied.

#### IP licensing

As companies have tried to get to market faster and others have attempted to specialize, the use of third-party IP has skyrocketed. This has created a huge hurdle in the form of licensing, which can be very complex and expensive to manage and monitor. Passing the burden of IP management on to the platform supplier can ease this pain.

#### Inventory

A POA can impact inventory in many positive ways. A well-designed platform can be quickly configured to meet the needs of multiple customers in custom configurations. For instance, a chipset supplier can build a single superset product in mass volumes while enabling specific features on demand as required by each customer. This allows the supplier to forecast an aggregate of parts instead of each individual configuration. This means less inventory, improved operational efficiency, and less price erosion because they are not trying to clear inventory.

#### 7" Touch Panel Computer for embedded GUI / HMI applications

quantity 1 pricing starts at \$449

- Low power, Industrial Quality Design

- Mountable aluminum frame

- # 64MB SDRAM (128MB opt)

- 512MB Flash w/ Debian Linux

- Programmable FPGA 5K LUT

- 7" Color TFT-LCD Touch-Screen

- 800x480 customizable video core

- Dedicated framebuffer 8MB RAM

- Audio codec with speaker

- Boots Linux 2.6 in about 1 second

- Unbrickable, boots from SD or NAND

- Runs X Windows GUI applications

- Runs Eclipse IDE out-of-the-box

- Over 20 years in business

- Never discontinued a product

- Engineers on Tech Support

- Open Source Vision

- Custom configurations and designs w/ excellent pricing and turn-around time

- Most products ship next day

See our website for our complete product line

We use our stuff.

visit our TS-7800 powered website at

www.embeddedARM.com (480) 837-5200

#### Debugging

Using a platform means that all of the modules do not need to be touched when troubleshooting. Platform components usually go through a rigorous debugging process before being deployed in many other related designs by other customers. POAs often have a better debugging interface that can make the whole process easier because it is designed with the complete platform in mind.

#### **Testing**

Many interfaces have industry test suites to ensure that the feature operates properly. For example, USB has test suites and compliance testing developed by the USB Implementers Forum. If the platform provider has completed the testing, this eliminates or reduces the need to test to the same level at the next step. In highly complex systems with many interfaces, this can save time and costs.

#### Standards and the ability to support changing standards

Organizations throughout the embedded community develop and evangelize standards necessary to the success of the industry. Platform suppliers are frequently key members of standards organizations, influencing the direction of the standard and ensuring its successful development. Many standards used in today's embedded devices are new or changing. Platform developers can reduce the burden on the design engineer by keeping track of the latest developments, incorporating them into the platform as they become available. You don't have to track all the nuances, develop solutions, and then figure out how to integrate and test.

#### Customizing

In reality, device manufacturers always need some level of customization because each device is a bit different. Well-developed POAs leave room for some degree of customization either by the customer or with the help of the platform provider. Many suppliers have design service teams that can be employed to add just the right degree of customization to help your product stick out in the market. Suppliers have the inside advantage because they know the platform well.

They use the input they receive from customers when assisting with customization to incorporate additional value in next-generation platforms.

#### Time to market

Anyone who has ever tried to round up, integrate, and test all the right pieces knows how much time can be saved using a well-developed POA. "It's important for manufacturers to be able to deliver products to market quickly, efficiently, and on budget," states Russell Harris, CEO of MontaVista Software. "By leveraging a platform like Montabello [Figure 2], our device customers can focus on building the best products, not developing a complex software infrastructure. Device manufacturers get a 6-12 month head start on their project, improving time to market and enabling them to realize significant development cost savings."

#### Lower cost

All of the previously mentioned benefits involve some cost-savings element. Learning how to take advantage of these benefits can maximize your investments.

**Figure 2 I** Montabello is a Linux-based software platform that offers an integrated set of applications for mobile Internet devices.

**Figure 3** I Windows Embedded POSReady 2009 helps transition Point-Of-Service (POS) systems from transaction processing to enhanced customer service.

#### Risk management

POAs can significantly reduce risks in your design. Many customers contribute to the platform architecture and expose it to a myriad of testing and usage scenarios that measure the design in ways you may not have considered. The platform supplier provides an additional level of expertise that you can lean on if you run into design issues.

#### Customer loyalty

Every vendor strives to develop a loyal base of customers, and POAs are an excellent way to develop that loyalty. All the benefits are evident to customers, and they show their appreciation by sticking with their suppliers. The pressure is on the suppliers to keep the platforms relevant and high quality.

"In an increasingly connected world, retail and hospitality businesses need technologies that help the transition from transaction processing to enhanced customer service and relationship building," asserts Ilya Bukshteyn, senior director of Windows Embedded marketing at Microsoft. "Windows Embedded POSReady 2009 [Figure 3] is specifically designed to help enable this transition. With Windows technologies such as Microsoft Silverlight, .NET Framework 3.5, and Windows

Presentation Foundation, the platform enables a differentiated and compelling user experience that can lead to greater customer loyalty."

#### The downside: Getting locked in

The disadvantages of POAs begin with getting locked into a particular platform containing a subcomponent that might not fully or correctly meet your product's needs. Changing a subcomponent can sometimes be difficult or impossible because of its integration into the POA. If you think this is going to be something that you may need to do during development, then you should ask if the platform components are interchangeable. This is where standards can provide assistance. Correct implementation of strategic standards can make subcomponents more interchangeable.

Sometimes the platforms have too little or too much functionality. Adding or deleting subcomponents can be very difficult or cost-prohibitive. Again, make sure to verify the platform architecture's scalability.

#### The future of platforms

"Platform design is the wave of the future," contends Bryan Lewis, semiconductor research VP for Gartner. "Design reuse, time to market, and risk management are of top importance to system designers in general and especially in this troubled economy. Platform design brings clear benefits to the market while controlling the cost for both chip suppliers and system designers."

Suppliers of components used in embedded computing devices will continue to roll out new platforms that are more specific to existing and future applications. Platforms have an untangible advantage that is difficult to measure with traditional ROI – the advantage of supplier focus. For suppliers to develop credible, industry-acceptable platforms, they must understand the market problems and needs on both sides of their position in the supply chain. Not having this knowledge prevents them from developing winning platforms.

Microsoft's Mike Hall, technical product manager for Windows Embedded, sees a strong future for platforms and is looking at new market segments to determine the next step. Platforms benefit everyone along the supply chain by easing the pain of integration and managing IP and licensing costs yet leaving the door open to quick customization that lets developers differentiate their products from the competition. **FCD**

## Protocol analyzers simplify USB debugging

By Etai Bruhis

USB devices look pretty simple to use – at least when they're working correctly. Embedded engineers need the right set of tools to manage the details of proper device operation. The following examples show how USB protocol analyzers can do just that.

The widespread integration of USB into embedded applications presents many developers with the challenge of using this protocol for the first time. The complexity of USB can mask problems, leaving issues that are difficult to detect and isolate when a USB device misbehaves.

USB protocol analyzers allow engineers to gain greater visibility into the bus and help them quickly pinpoint the exact nature of a bug, whether it is in the physical, electrical, or protocol layer. Exploring how a USB protocol analyzer can be used to debug potential problems encountered in USB development shows how this can be accomplished.

#### **Comparing tool options**

Faced with a wide selection of debugging tools such as logic analyzers, oscilloscopes, and protocol analyzers, finding the ideal debugging tool can be a daunting task. Fortunately, the complexity of USB guides the choice of a suitable debugging solution.

As a result of this complexity, tools like logic analyzers or oscilloscopes may be limited by their low-level view, making

it difficult to sort through large amounts of serial data. On the contrary, protocol analyzers can nonintrusively monitor the bus, view data as packets, and capture higher-level protocol-specific data in large volumes.

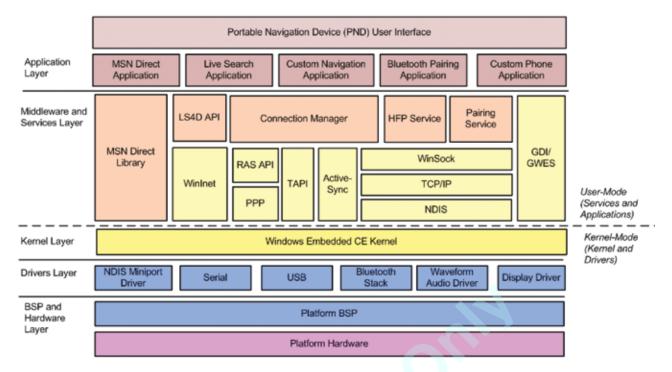

The setup for capturing USB data is a straightforward process. In Figure 1, the USB analyzer is connected in-line between the target host and the target device to nonintrusively capture data. While the target host and target device

communicate with one another, the analyzer logs all of the bus traffic. Some analyzers store this data and display it once the capture is complete; others display and analyze the data in real time, as it is occurring on the bus.

In contrast with scopes and logic analyzers, USB capture software can display detailed information such as time stamp, device and endpoint address, Packet Identifiers (PIDs), and data in a human-readable format. The software also includes search and/or filter features to help developers quickly locate data of interest within a large amount of data.

The following examples demonstrate how a USB protocol analyzer can be used to help identify common problems in USB development.

#### **USB** data validity

USB employs two error-checking methods to ensure that data is sent correctly. A Cyclic Redundancy Check (CRC) is sent with all data transmissions to validate data integrity within a packet.

In addition, a toggle bit is encoded in the data packet's PID to guarantee that packets are sent in the correct sequence. Correct data sequencing is especially important when attempting to transfer large files across multiple independent USB transmissions.

When transferring data over multiple packets, the data PID typically toggles between DATA0 and DATA1 on each consecutive successful transmission. As data is successfully transmitted, implying that the CRC is valid, the receiver acknowledges (ACK) the data, and both transmitter and receiver toggle their DATA bit. However, if there is a data error and the CRC check fails, the receiver will not reply with an ACK, and the transmitter will resend the data with the same toggle bit. The transmitter will continue to resend the same data with the same toggle bit until the receiver acknowledges its reception.

In some cases, the data is sent correctly, but the ACK handshake gets corrupted on the bus. When this occurs, the receiver

**Figure 1** I In a typical device configuration for capturing USB data, the USB analyzer is connected between the target host and target device.

#### Feature: Chip and board debugging

thinks that the data was sent properly and updates its toggle bit, but the transmitter does not actually know if the data was received correctly. Therefore, the transmitter will send the same data with the same toggle bit. Since the toggle bit has not changed, the receiver assumes that this is a retransmission of the same data and silently ignores the data. The receiver will then ACK, causing the transmitter's toggle bit to update correctly.

#### Finding problems in data bit toggling

Incorrectly handling the toggle bit is a common USB problem that is hard to identify because the symptoms do not necessarily render a device unusable. A device may simply appear to have a reduced throughput, or individual data transmissions may be dropped. Without the aid of a hardware protocol analyzer, it is nearly impossible to deduce that improper data toggling is the cause of the problem.

To illustrate this issue, consider a situation where a host side application is failing to receive any data from the device. To help in the debugging process, the device is configured to send a counter value that is updated with each successful transmission. The root of the problem can be traced to a variety of bugs related to firmware, software, and/or hardware.

Using a hardware protocol analyzer can quickly pinpoint this type of error. In Figures 2 and 3, data is being captured from two devices; one is functioning properly and the other is not. In both cases, it is clear that low-level hardware is functioning correctly, as valid data is being transmitted without CRC errors. To

| Sp | m:s.ms.us    | Len | Err | Dev | Ep | Record       | Data                 |

|----|--------------|-----|-----|-----|----|--------------|----------------------|

| HS | 0:00.100.011 | 7 B |     | 01  | 02 | DATA0 packet | C3 00 00 00 00 FF DB |

| HS | 0:00.100.023 | 7 B |     | 01  | 02 | DATA0 packet | C3 01 00 00 00 FE 27 |

| HS | 0:00.100.035 | 7 B |     | 01  | 02 | DATA0 packet | C3 02 00 00 00 FE 63 |

| HS | 0:00.100.046 | 7 B |     | 01  | 02 | DATA0 packet | C3 03 00 00 00 FF 9F |

| HS | 0:00.100.058 | 78  |     | 01  | 02 | DATA0 packet | C3 04 00 00 00 FE EB |

| HS | 0:00.100.070 | 7 B |     | 01  | 02 | DATA0 packet | C3 05 00 00 00 FF 17 |

Figure 2 I The consecutive DATA0 PIDs in the record column show that the device is not toggling its data PID.

| Sp | m:s.ms.us    | Len | Err | Dev | Ep | Record       | Data                 |

|----|--------------|-----|-----|-----|----|--------------|----------------------|

| HS | 0:00.100.011 | 7 B |     | 01  | 02 | DATAO packet | C3 00 00 00 00 FF DB |

| HS | 0:00.100.023 | 7 B |     | 01  | 02 | DATA1 packet | 4B 01 00 00 00 FE 27 |

| HS | 0:00.100.035 | 7 B |     | 01  | 02 | DATA0 packet | C3 02 00 00 00 FE 63 |

| HS | 0:00.100.046 | 78  |     | 01  | 02 | DATA1 packet | 48 03 00 00 00 FF 9F |

| HS | 0:00.100.058 | 78  |     | 01  | 02 | DATA0 packet | C3 04 00 00 00 FE EB |

| HS | 0:00.100.070 | 7 B |     | 01  | 02 | DATA1 packet | 48 05 00 00 00 FF 17 |

**Figure 3** I The alternating DATA0 and DATA1 PIDs show proper toggling between subsequent packets.

aid in the analysis, software display filters are used to display only DATA packets, as shown in Figures 2 and 3.

Upon inspection, it is obvious that while one device did not toggle the data PID (Figure 2), the other one did toggle the data PID after each packet (Figure 3). As discussed earlier, sequential DATA0s should not be passed to the application because the receiver will ignore packets that repeat the same toggle bit. This explains why data is not being passed to the application. However, the reason why the same toggle bit is being used is still unknown.

To investigate this issue further, the entire transaction sequence can be examined (Figure 4). In this view, it is clear that the transaction is completing successfully because the capture shows the ACK for each data packet, but the DATA bit is not toggling. Furthermore, transmissions that use sequential toggle bits are supposed to resend identical data.

Because the device in this case continues to update its counter, the firmware must be processing the ACK from the host. The error therefore lies in the handling of the DATA toggle within the device. Specifically, the firmware is not toggling the bit on each successful transmission. Without a hardware protocol analyzer, this small mistake could take days or weeks for a developer to fix.

#### Low-level bus events

Another common error occurs with lowlevel bus events. The USB specification defines a number of crucial bus-level signaling events that follow specific timing criteria and determine such things as suspend, resume, and the high-speed handshake. Mistakes during these events can cause a number of errors, including a host's failure to recognize the device. These types of events are difficult if not impossible to debug without the aid of a hardware tool.

As an example, the high-speed hand-shake requires the host to issue a minimum of three pairs of alternately driven D- (Chirp K) and D+ (Chirp J) for 40-60 microseconds. Even though the USB specification only requires three pairs for this chirp sequence, hosts will often send hundreds of them. While it is possible to use a scope to measure this sequence of events and calculate durations with the cursors, utilizing engineering time to verify each chirp with a scope is a tedious and error-prone process. A hardware protocol analyzer, in contrast,

#### High-speed USB 2.0 monitor

The examples in this article were generated using the Beagle USB 480 Protocol Analyzer, a low-cost, nonintrusive, high-/full-/low-speed USB 2.0 bus monitor that can capture, display, and filter USB traffic and bus states in real time. An onboard 64 MB buffer ensures that sustained bursts of 480 Mbps traffic can be captured with no data loss. Other major features include On-The-Go support, automatic speed detection, hardware-based packet suppression, and multiple digital inputs and outputs for synchronization with external logic.

This protocol analyzer is compatible with Windows, Linux, and Mac OS X and comes with free software, API, updates, and technical support.

| Sp | m:s.ms.us    | Len | Err | Dev | Ep | Record                        | Data                 |

|----|--------------|-----|-----|-----|----|-------------------------------|----------------------|

| HS | 0:00.100.010 | 48  |     | 01  | 02 | ♥ Ø IN txn                    | 00 00 00 00          |

| HS | 0:00.100.010 | 3.8 |     | 01  | 02 | O IN packet                   | 69 01 C1             |

| H5 | 0:00.100.011 | 7 B |     | 01  | 02 | III DATAO packet              | C3 00 00 00 00 FF DB |

| HS | 0:00.100.013 | 18  |     | 01  | 02 |                               | 02                   |

| HS | 0:00.100.021 | 48  |     | 01  | 02 | ♥ 🥑 IN txn                    | 01 00 00 00          |

| HS | 0:00.100.021 | 3 B |     | 01  | 02 | O IN packet                   | 69 01 C1             |

| HS | 0:00.100.023 | 7 B |     | 01  | 02 | DATAO packet                  | C3 01 00 00 00 FE 27 |

| HS | 0:00.100.025 | 18  |     | 01  | 02 |                               | 02                   |

| HS | 0:00.100.033 | 48  |     | 01  | 02 | ♥ 🥑 IN txn                    | 62 66 60 60          |

| HS | 0:00.100.033 | 3 B |     | 01  | 02 | <ul> <li>IN packet</li> </ul> | 69 01 C1             |

| HS | 0:00.100.035 | 78  |     | 01  | 02 | DATA0 packet                  | C3 02 00 00 00 FE 63 |

| HS | 0:00.100.036 | 18  |     | 01  | 02 |                               | 02                   |

**Figure 4** I An expanded view of the transaction shows new data being sent with the same DATA toggle bit.

| Sp  | m:s.ms.us    | Len     | Err | Dev | Ep | Record                                | Data                                                    |

|-----|--------------|---------|-----|-----|----|---------------------------------------|---------------------------------------------------------|

| FS  | 0:00.107.526 | 50.0 us |     |     |    | ₩ <k chirp=""></k>                    |                                                         |

| FS  | 0:00.107.576 | 50.0 us |     |     |    | ↓  ∠  J chirp>                        |                                                         |

| FS: | 0 00 108 026 | 30.0 us | U   |     |    | Bus event                             | <reset> / <k chirp=""> / <tiny k=""></tiny></k></reset> |

| FS  | 0:00.108.056 | 50.0 us |     |     |    | ₹ <j chirp=""></j>                    |                                                         |

| FS  | 0:00.108.106 | 5.05 ms |     |     |    | ♥ # [50 K-] Chirp Pairs ] [1 K Chirp] |                                                         |

| FS  | 0:00.108.106 | 50.0 us |     |     |    | ≪K chirp>                             |                                                         |

| FS  | 0:00.108.156 | 50.0 us |     |     |    |                                       |                                                         |

| FS  | 0:00.108.156 | 50.0 us |     |     |    | de <) chirp>                          |                                                         |

**Figure 5** I The highlighted row shows an unexpected bus event halfway through the chirp sequence.

can save time by automatically measuring each signal and indicating potential errors. Furthermore, with an analyzer, these measurements can be done on every test run, thus automatically catching new or intermittent bugs.

In Figure 5, the capture software highlights an error with a mistimed chirp sent from a USB host under development. In this particular example, the mistake occurred halfway through the chirp sequence, and a cursory look on a scope would have missed it. The consequences of such an error are undetermined as this is out of spec, and any number of processes could malfunction.

While it is possible that a device is robust enough to handle this situation and can continue to function properly, other devices may be more sensitive to the out-of-spec signaling. If internal testing was only run with a small subset of devices that all passed, a developer without a hardware protocol analyzer may never know that such an error exists. A malfunctioning product could be sent out to the field, where the error would be exposed later – to the frustration of many customers. By using a hardware-based analyzer, engineers can avoid escalated costs due to unforeseen errors.

#### Quick and easy troubleshooting

The development and debugging stage is a crucial step in the product life cycle. As the aforementioned situations illustrate, using a hardware-based USB protocol analyzer presents the data packets of a complicated protocol such as USB in an accessible and human-readable format. Using an analyzer, engineers can easily test their applications and quickly identify problem areas while reducing development time and simplifying the debugging process. **ECD**

Etai Bruhis is an engineer for Total Phase, based in Sunnyvale, California, where he specializes in hardware development. He

graduated magna cum laude from the University of California at Berkeley with a Bachelor's degree focusing on Mechanical and Electrical Engineering.

Total Phase 408-850-6500 sales@totalphase.com www.totalphase.com

## Software Bill of Materials improves Intellectual Property management

By Mahshad Koohgoli, PhD, and Sorin Cohn-Sfetcu, PhD

Accurate record keeping and proper Intellectual Property (IP) management enhances embedded system development throughout the design chain and ensures more effective product life-cycle support.

Software has become a ubiquitous part of cell phones, cameras, computers, and other mass-distributed consumer products. This pervasiveness can hinder embedded system developers given that software development costs sometimes outweigh those of hardware development, and product support issues are more often related to software rather than hardware problems.

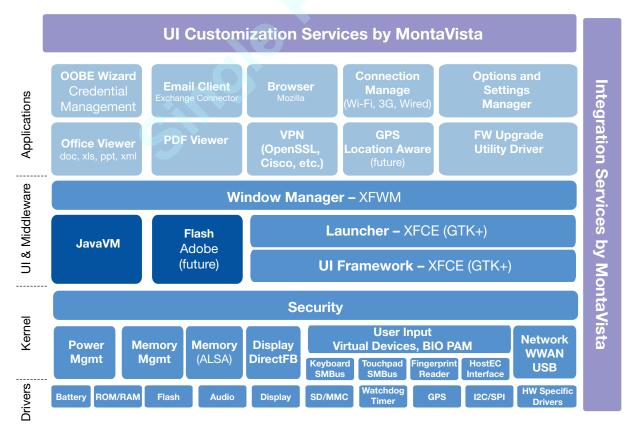

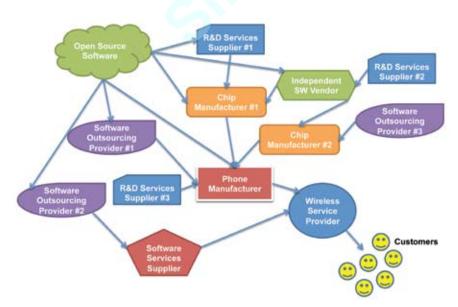

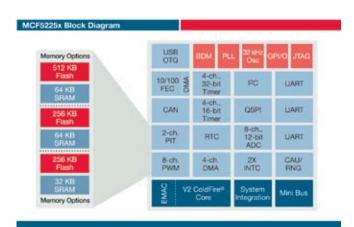

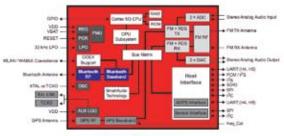

However, embedded developers can reduce software development costs and schedules through software reuse, reliance on third-party code, and increasingly, open source code. Indeed, companies rarely create all of the software in their products. Much of the code is independently developed by the sources mentioned and then integrated into the final product with various degrees of value added throughout the development cycle. The cell phone example illustrated

in Figure 1 demonstrates this integration and value-add process.

The cell phone combines software developed by the manufacturer and outsourced developers as well as the software that comes with the chipsets, which are typically developed in-house or acquired from third parties or open source directly or through various layers of chained suppliers.

An end product – in this case, the cell phone – is thus the sum of the code provided by the many organizations and individuals involved in the overall cell phone software supply chain. However, an end product rarely provides a complete and up-to-date view of all of these contributors and their respective software components. This can lead to increased

costs, delayed schedules, and significant business risks if any of the software components do not meet proper IP and copyright obligations or if they have to be corrected once the product reaches the market. Imagine that a security fault is discovered in the protocol stack supplied by one of the players. Not only would it be difficult to ascertain which of thousands of products are affected, it would also be extremely tedious and costly to find a solution and correct the problem.

These issues would not exist if the soft-ware code came with proper records and pedigrees for all of its components. Few companies have managed to capture and deliver a software Bill of Materials (BOM) because until recently, most methods for determining what is in the code and ensuring correct IP management were retrospective; companies used either cumbersome manual audits or expensive tools for automatic code analysis. Such after-the-fact corrective methods can result in costly redesigns and delays in product availability.

#### Automatic tools check code history

Embedded developers can avoid these problems by adopting real-time record gathering and preventive IP management processes. To accomplish this, companies must set acceptable software adoption and IP policies and use newly released automatic tools to analyze, record, and compliance-check legacy code as well as any new code brought into the project.

Good software development practices have evolved to include systems for

**Figure 1** I The software code in a cell phone is provided by multiple parties involved in the product development cycle.

checking syntax, managing software versions, and tracking software bugs. Nonetheless, certain disciplines that are accepted practice in structured hardware development have yet to be adopted in software development:

- An approved vendor list that contains the approved components and licenses, including commercial terms, vendor history, versions, and pricing so that a developer can select components from the list without concern

- Automatic notification when someone tries to use code with unapproved licenses or code modules governed by incompatible licenses

- A BOM that fully records which components are used in the final product, including details to enable production, determine costs, identify where it can be exported, and track vendor upgrades and other postdesign activities

The best approach is to make record keeping and source code IP management an integral part of the software development and quality assurance processes.

Automatic tools are now available to handle these tasks in an unobtrusive manner and with minimal training, enabling project managers to define appropriate policies for record keeping, source code adoption, and IP management. For example, tools like Protecode's Enterprise IP Analyzer can be applied to existing (legacy) code for establishing an up-to-date map of its components and their pedigrees. Another tool, the Development IP Assistant, is integrated within specific development environments, where it operates unobtrusively in the background at each development workstation to detect, log, and identify in real time each piece of code brought by the developer into the respective project.

These tools check the attributes of each piece of code against the adoption and IP management policy for the project and take appropriate action according to the established policy. Furthermore, these tools provide a software BOM that enables developers and clients throughout the embedded system design chain to be fully cognizant of what is in the code and how to address support issues effectively.

Applying real-time record keeping and preventive IP management reduces development costs, avoids wasted resources in after-the-fact corrective activities, shortens development cycles, and enhances the overall lifelong value of embedded software systems. **ECD**

Sorin Cohn-Sfetcu works in the marketing department at Protecode. He has 30 years of international business and technology experience and holds several

patents in Web services, wireless, and digital signal processing. Sorin has an MSc in Physics from the University of Calgary, an MEng in Engineering Physics from the Polytechnic Institute of Bucharest, and a PhD in Electrical Engineering from McMaster University in Canada.

Mahshad Koohgoli is the CEO of Protecode, based in Ottawa, Ontario, Canada. He has more than 25 years of experience in the telecommunications

industry and specializes in technology start-up businesses. Mahshad has a BSc and a PhD in Stochastic Control Processes from the University of Sussex, England.

Protecode

Sorin: 613-301-0066 scohn@protecode.com Mahshad: 613-721-5936 koohgoli@protecode.com www.protecode.com

# The high price of low-cost FPGA development boards

Low-cost FPGA development boards are a convenient option when starting a new project, but that choice carries a sting in its tail. These boards automatically constrain engineers' design options before they even start, forcing them to design in a fixed and predefined way that ultimately costs more money. As an alternative, designers should consider using a vendor-independent hardware development system that also communicates with the design software, resulting in a flexible, real-time development system that does not stifle innovation by restricting choices.

#### An expedient choice that bites back

A major challenge for any business, particularly in the current economic climate, is determining how much to invest in staff and equipment to achieve profitability goals. While overspending can wipe out potential increases in profit, underinvestment leaves companies ill-equipped to capitalize on market possibilities or even exposed to the risk of not achieving them.

Good business is all about finding the right investment-versus-results balance, making informed choices, and working toward fulfilling the company's needs in smarter ways. For the most part, companies both large and small accomplish this balancing act successfully. This frees them to focus on fine-tuning the corporate machine so that its long-term performance matches all those squiggly PowerPoint graphs business leaders are so fond of.

But in the electronics design industry, the rise of programmable devices such as FPGAs has unearthed an aberration in this normally sensible industry behavior. That quirk comes as a result of the FPGA development hardware and tools selection process, in which the usually thorough considerations of cost versus results,

long-term implications, and workflow efficiency often take a holiday and are replaced by an equipment choice based on short-term expediency.

That convenient and often impulsive choice is a basic FPGA development board that costs about \$49 and is supported by free development tools from the FPGA device vendor.

#### The cost of convenience

Although a \$49 FPGA development board is undeniably attractive, it is nonetheless a curious and risky choice when placed in the framework of professional product design economics.

For example, say that a new product has a development cost of at least \$1 million as well as potential revenue of more than \$10 million, and is being designed by an engineer with a salary of \$100,000 – not uncommon figures in today's industry. Considering that an extremely critical part of this multimillion-dollar development is consigned to a system investment of \$49, these figures look somewhat misbalanced and even disturbing.

While it appears that the usual checks and balances failed in this case, they probably didn't; they just never happened, perhaps because a designer opportunistically decided that the \$49 board could

do the job, given that it has a suitable FPGA device, some useful peripherals, and a bunch of external connectors. The matching design tool set is a free download, so by making this quick decision, the designer can get cracking on embedded hardware development and embedded software developers can get one step closer to testing on real hardware.

On the surface this might seem like a reasonable solution to an immediate need, but in a professional design project where thousands or even millions of dollars are at risk, that unchecked decision carries a sting in its tail. Along with the quality limitations one might expect from a \$49 piece of development hardware, the real "gotcha" is that the range of possible design choices is vastly reduced by the built-in constraints of that system. These limitations are likely to cause costly design compromises and delays.

One constraint is the fixed FPGA device on the board, which narrows the design path to that device family and vendor. An initial decision of selecting a device that has excess capacity means engineers won't run out of gates or I/O, but all other device capabilities and features must be accurately predicted before serious design can begin.

If designers get that choice wrong – the device turns out to be too slow, uses too much power, needs a hard-coded processor or DSP, or has been superseded – there's no other option but to look for an alternative device and a new development board. The new board might only cost another \$49, but little of the existing design work can be transferred to the new device. This forces a substantial redesign and a costly delay in project development.

That scenario assumes that designers can source a suitable alternative device from the same vendor, but the situation is even worse if the only viable option is an FPGA from a different vendor. In this case, the incompatibility of the new device architecture means a total redesign and additional delays and cost. And all this time, the embedded software engineers are still waiting for the embedded hardware to arrive.

Another perhaps less obvious constraint is the free proprietary tool chain provided by FPGA vendors. While these tools are developed to support the vendor's products and encourage sales, they are understandably devoid of support for competitors' products. So if engineers change the FPGA device supplier to solve their design problems, they will also need to adapt to a new set of tools and methodologies.

All these factors add up: Designers have much less chance finding an optimal design solution; the change in device type forces a substantial redesign; switching vendors requires that designers learn new tools and methodologies; and above all, the outcome of a design project that potentially involves millions of dollars is placed at risk. In short, what was an expedient and possibly impulsive choice of development hardware turns out to be a decision that can severely compromise engineers' ability to explore design options for that project.

#### A sticky issue

In practice, the creeping truth is that the \$49 approach has also created a strong motivation for designers to stick with that particular vendor and device family to avoid extra work and delays. The more designers use devices and IP from that supplier in subsequent designs, the more their collective design resources become narrowly locked to that vendor.

This means that the lack of design choice within a given project and the compromises it introduces spread virally through future designs. Reusing vendor-centric designs in subsequent projects narrows the possibilities from the beginning, so engineers tend to adapt the design to suit the vendor's FPGA rather than selecting an FPGA that best suits the design, effectively locking into one restrictive design path.

It's also likely that engineers source IP cores from the device vendor as a convenient kick start to their designs. That IP is only useful with a specific range of FPGA devices from that particular vendor, so it is stuck to a reduced range of silicon. This *sticky IP* compounds the issue of limited design choice by stopping designers from jumping between devices supplied by

#### Feature: Programmable logic

different vendors when they are exploring design options.