## EMPERICA COMPUTING DESIGN

## If you need a powerful PC with fanless operation, choose WinSystems' EBC-855.

This extended temperature, high-performance, x86-based SBC operates Linux, Windows XP embedded, and other RTOSes to provide a seamless development platform. It also supports popular video and wired/wireless network standands.

#### EBC-855 features include:

- Intel® 1 GHz ZCD CPU or 1.8 GHz Pentium® M

- Intel® Extreme Graphics 2 technology supports CRT & LVDS flat panels simultaneously with dual independent displays

- Custom splash screen on start up

- 10/100 Mbps Intel® Ethernet controller

- 802.11a/b/g wireless supported

- 4 serial COM ports and 4 USB 2.0 ports

- 48 bi-directional TTL digital I/O lines

- Bi-directional LPT port

- Two EIDE ports (UDMA100) for hard disk

- 3.5-in. floppy disk drive and CompactFlash supported

- PC/104 and PC/104-Plus connectors

- Onboard AT keyboard and FDC controller

- AC97 six channel 5.1 surround sound

- +5 volt only operation

- EBX-size: 5.75" x 8.0" (146mm x 203mm)

- Industrial temperature operation

- Long-term product availability

- Off-the-shelf delivery

Contact us for additional information or OEM pricing. Our factory application engineers look forward to working with you.

Call 817-274-7553 or Visit www.winsystems.com/EBC-855 Ask about our 30-day product evaluation

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

Volume 6 • Number 4

www.embedded-computing.com

#### Columns

#### 8 Editor's Foreword

Multi to the core

By Jerry Gipper

#### 10 Technology Passport

**Electronic firefighting**

By Hermann Strass

#### 12 Consortia Connection

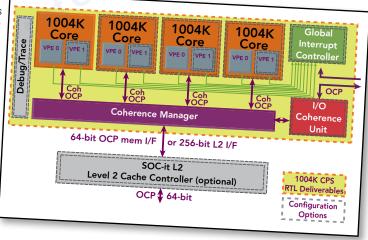

Expanding multicore, RapidIO, and mobile platform innovation

14 Ingenuity @ work

Filtering out software side effects

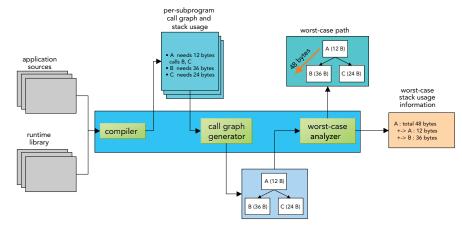

#### Departments

#### 44 Editor's Choice Products

By Jerry Gipper

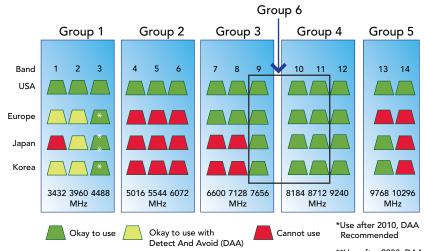

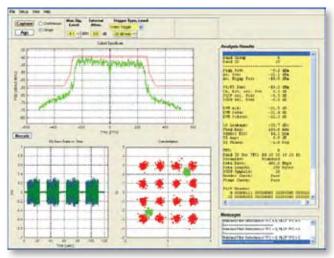

#### 40 Real-world Certified Wireless USB testing

By Onno Harms and Rob Brownstein, LitePoint

#### Cover/Web Resources/Events

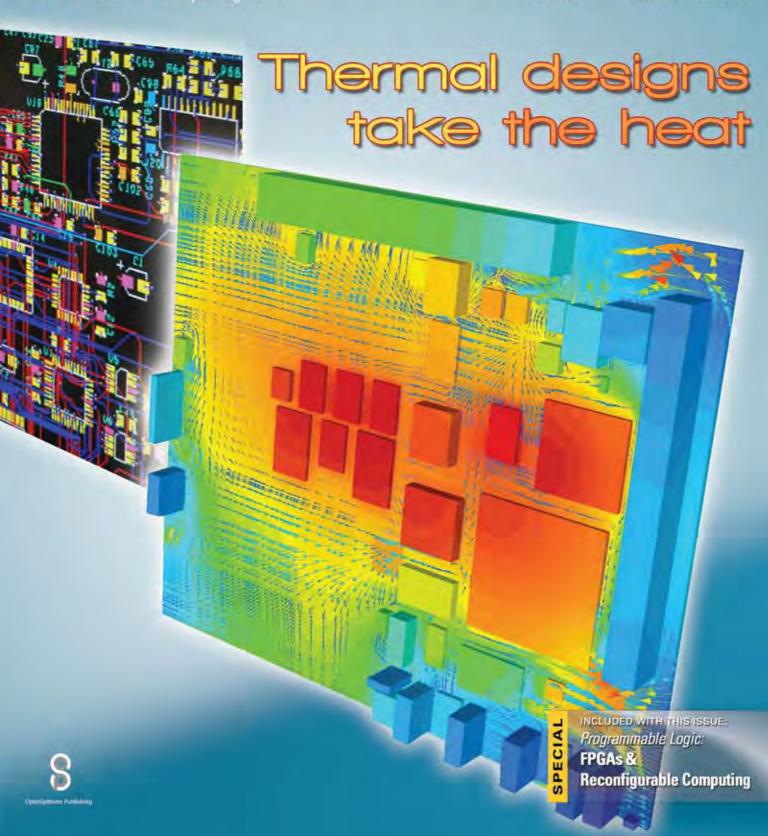

#### On the cover

Innovative thermal management methods described in this issue are improving heat dissipation while meeting performance demands in embedded designs. PCB thermal analysis photos on cover and page 24 courtesy of Flomerics, www.flomerics.com

#### **E-casts** www.embedded-computing com/ecast

SDR is more than JTRS: Think military wireless networks and civilian mobile infrastructure

May 21, 2 p.m. EDT

#### E-letter

www.embedded-computing.com/eletter

SoC microcontrollers power portable medical device innovation By Kevin Belnap, Texas Instruments

#### **Web Resources**

#### Subscribe to the magazine or E-letter at:

www.opensystems-publishing.com/subscriptions

#### **Industry news:**

Read: www.embedded-computing.com/news

Submit: www.opensystems-publishing.com/news/submit

#### Submit new products at:

www.opensystems-publishing.com/np

#### **Events**

#### **NXTcomm**

June 16-19 • Las Vegas, NV www.nxtcommshow.com

Hardware

#### **Features**

#### Special Feature

- 16 Packing heat

... into reusable energy

By John Lin, VIA Technologies

- 20 Switching strategies for increasing processor power efficiency

By Brian Law and Greg Ferrell, Fairchild Semiconductor

# Thermal simulation optimizes cooling in high-performance systems By Kevin Rhoades, Kontron America Thermal concepts enhance DRAM memory subsystem designs By Phan Hoang, Virtium Technology

#### Software

32 Virtual channels accelerate traffic in Serial RapidIO 2.0

By David MacAdam and Robert Bishop, IDT

36 Virtual hardware platforms: Productivity-proven for software development

By James Clough, RadioFrame Networks

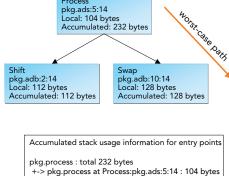

38 Don't blow your stack: Static stack analysis for high-integrity systems By José F. Ruiz, PhD, AdaCore

## We've Slashed Slow **Boot-Up Times**

We don't pussyfoot around. Your embedded application needs to come up and execute quickly. Micro/sys CPU boards are optimized to cut through the boot code, which slashes the time from start-up to application readiness for maximum performance over a wide range of hardware platforms.

When you use Micro/sys boards, you gain the value of more than 30 years experience in embedded applications. Our sales team will help you match your boot time requirements with the best board, BIOS, and operating system combination. If you have a tough spec, give us a call .... We welcome the challenge.

MCB58: Compact microcontroller with CAN, 32 DIO, 4PWM D/A. Temp. Sensor, RTC, 16K Serial EEPROM, 60K Flash, and 4K RAM. Boots in 160 microseconds.

SBC1586: Headless, Low-Power PC/104 Pentium with Compact. Flash, 4 COM ports, USB, and Ethernet. Boots in under 4 seconds.

3730 Park Place, Montrose, CA 91020 Voice (818) 244-4600 Fax (818) 244-4246 info@embeddedsys.com

IICRO/SYS

SBC1625: Low-Power ARM processor with Dual Ethernet, 4 COM ports and 24 Digital I/O on PC/104. Boots in under 14 seconds to Linux Prompt.

SBC4495: 486/586 EPIC CPU with GPS, Ethernet, 24 bit I/O, 14 bit A/D and D/A. Boots in under 4 seconds:

www.embeddedsys.com

©2006 Micro/sys. All brand and/or product names listed are registered trademarks of their respective owners.

### TS-7800 High-End Performance with Embedded Ruggedness

\$269 qty 1

\$229 qty 100

500 MHz ARM9

- New unbrickable design- 3x faster

- Backward compatible w/ TS-72xx

- Low power 4W at 5V

- **128MB DDR RAM**

- 512MB high-speed onboard Flash

- 12K LUT user-programmable FPGA

- Internal PCI Bus, PC/104 connector

- 2 USB 2.0 480 Mbps

- Gigabit ethernet

2 SD sockets

- 10 serial ports

110 GPIO

- 5 10-bit ADC 2 SATA ports

- Sleep mode uses 200 microamps

- Boots Linux in < 2 seconds

- Linux 2.6 and Debian by default

Design your solution with one of our engineers

- Over 20 years in business

- Never discontinued a product

- Engineers on Tech Support

- Open Source Vision

- Custom configurations and designs w/ excellent pricing and turn-around time

- Most products stocked and available for next day shipping

See our website for options, peripherals and x86 SBCs

We use our stuff.

visit our TS-7200 powered website at

www.embeddedARM.com (480) 837-5200

## Embedded COMPUTING D E S I G N

#### **Embedded and Test & Analysis Group**

- **■** Embedded Computing Design

- Embedded Computing Design E-letter

- Embedded Computing Design Resource Guide

- Industrial Embedded Systems

- Industrial Embedded Systems E-letter

- Industrial Embedded Systems Resource Guide

- Unit Under Test

- Unit Under Test E-letter

Editorial Director Jerry Gipper

jgipper@opensystems-publishing.com

Contributing Editor Don Dingee

Senior Associate Editor Jennifer Hesse

jhesse@opensystems-publishing.com

Assistant Editor Robin DiPerna

European Representative Hermann Strass

hstrass@opensystems-publishing.com

Special Projects Editor Bob Stasonis

Art Director

Senior Designer

Graphic Coordinat r

Senior Web Developer

Web Content Specialist

Art Director

David Diomede

Joann Toth

Sandy Dionisio

Konrad Witte

Matt Avella

Circulation/Office Manager Phyllis Thompson

subscriptions@opensystems-publishing.com

#### **OpenSystems Publishing**

Editorial/Production office:

16872 E. Avenue of the Fountains, Ste 203, Fountain Hills, AZ 85268

Tel: 480-967-5581 ■ Fax: 480-837-6466 Website: www.opensystems-publishing.com

Publishers John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial Rosemary Kristoff

#### **Communications Group**

Editorial Director

Managing Editor

Senior Editor (columns)

Technology Editor

European Representative

Joe Pavlat

Anne Fisher

Terri Thorson

Curt Schwaderer

Hermann Strass

#### Military & Aerospace Group

Group Editorial Director

Associate Editor

Senior Editor (columns)

Senior Associate Editor

European Representative

Chris Ciufo

Sharon Schnakenburg

Terri Thorson

Jennifer Hesse

Hermann Strass

ISSN: Print 1542-6408, Online 1542-6459

**Embedded Computing Design** is published 8 times a year by OpenSystems Publishing LLC., 30233 Jefferson Ave., St. Clair Shores, MI 48082.

Subscriptions are free to persons interested in the design or promotion of embedded computing systems. For others inside the US and Canada, subscriptions are \$56/year. For 1st class delivery outside the US and Canada, subscriptions are \$80/year (advance payment in US funds required).

Canada: Publication agreement number 40048627 Return address: WDS, Station A, PO Box 54, Windsor, ON N9A 615

POSTMASTER: Send address changes to **Embedded Computing Design** 16872 E. Avenue of the Fountains, Ste 203, Fountain Hills, AZ 85268

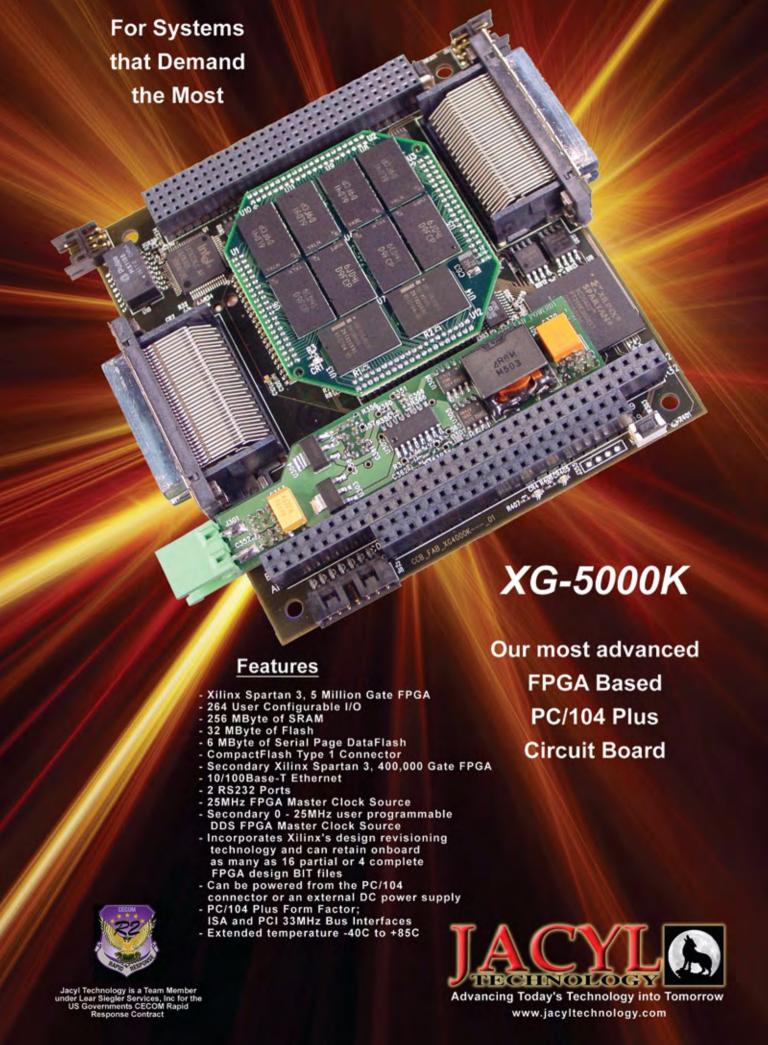

## Annapolis Micro Systems The FPGA Systems Performance Leader

## WILDSTAR 5 for IBM Blade The Perfect Blend of Processors and FPGAs

Fully Integrated into IBM Blade Management System

Abundant Power and Cooling Ensure Maximum Performance

Made in the USA

#### **Ultimate Modularity**

From 2 to 8 Virtex 5 FPGA/Memory Modules Input / Output Modules Include: Quad 130 MSps thru Quad 500 MSps A/D 1.5 GSps thru 2.2 GSps, Quad 600 MSps A/D Dual 1.5 GSps thru 4.0 GSps D/A Infiniband, 10 G Ethernet, FC4, SFPDP

Direct Seamless Connections with no Data Reduction

Between External Sensors and FPGAs

Between FPGAs and Processors over IB or 10GE Backplane

Between FPGAs and Standard Output Modules

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com (410) 841-2514 www.annapmicro.com

## Editor's Foreword

#### Multi to the core

Jerry Gipper

Multiple processor systems have been around for decades. System architects have designed single computers with thousands of processors, and multicore processors have continually showed up in various niche applications like DSPs.

Today, though, it is different. Multicore processors are the mainstream method for processor development. Given that highperformance processor designers have hit the wall on power consumption, moving to multiple core processors is the most practical way to continue improving processor performance while maintaining a manageable power budget. Multicore is a way past the performance plateau. Embedded platform designers have no choice but to learn to use these multicore processors, and they will need to modify their applications to take full advantage of multiple cores.

One resource that can help engineers is the Multicore Association. I recently attended the group's Multicore Expo, an event that showcased a mix of sponsors from both the high-performance and embedded computing segments. While the high-performance segment has years of experience using multiprocessors, it is a new frontier for many in the embedded segment.

During a panel session on the future of multicore, Jon Peddie of Jon Peddie Research (www.jonpeddie.com) commented that not much has changed in the past 30 years and predicted that not much more will change in the next 5 years. Most of the presenters supported this position in their sessions.

The high-performance segment has implemented Symmetrical Multiprocessing (SMP) solutions where the multicore architecture is a natural fit. In that segment, everyone agrees that the best way to get the most out of every clock cycle in a multiprocessor or multicore system is to structure the application and data set to run in parallel so that every processor or core is busy all the time. Unfortunately, only certain applications lend themselves to a parallel structure, most notably image processing and simulation modeling. This has not changed since the conception of parallel computing. What has changed is that the size of processing elements has expanded and GFLOP numbers have increased two or three orders of magnitude higher.

In these environments, multiple cores are running multiple operating systems or multiple threads within an application. This is the hot spot for typical embedded applications that have many dependent and independent tasks running at the same time on a single platform.

AMP embedded applications often use combinations of homogeneous and heterogeneous cores. Many Systems-on-Chip (SoCs) are multicore but have heterogeneous cores for specific functions. One core may be the general-purpose processing core and other cores may be optimized to process I/O or provide DSP functionality Some newer parts are even introducing dual or quad homogeneous multicore for general-purpose processing with an extra heterogeneous core for specialized functions.

As more players enter the multicore processor market, we will observe more divergence with no convergence in sight despite efforts like the Multicore Association's Multicore Communications API (MCAPI) announced at the Multicore Expo. This will pose a challenge for system developers because their choices will not be compatible, complicating design changes and forcing developers to make decisions that will prevent platforms from being as portable between iterations as they desire.

Numerous similar but distinct topics are covered under the word "multicore." Designers shouldn't be frightened off by the term. It is forecasted that by 2010 nearly 100 percent of processors shipped will be multicore. Kerry Johnson of QNX summed up this trend as he pointed out the variety of options available to embedded systems designers. Most applications will work well with multicore processors, requiring no changes to the software and enabling designers to start moving applications now. Later, they can work out more optimized changes to their system architectures to truly gain from multicore processors.

Feel free to share your comments via e-mail or visit our blog at www.embedded-computing.com to add your comments.

Jerry Gipper, Editorial Director jgipper@opensystems-publishing.com

Despite these challenges, designers are making progress in two areas: Asymmetrical Multiprocessing (AMP) and virtualization.

Check out the recent E-cast, "Maximizing Performance on Intel Multicore Processors," cosponsored by QNX and Intel.

Download it now at www.opensystems-publishing.com/ecast

## Embedded Computer Solutions For Harsh Environments

-40°C to +85°C Operating Temperature

Five Year Product Availability

Guarantee

World's Fastest Embedded Computer Module

## Computer Modu

2.8 GHz Pentium 4

(Low power 1,6Ghz and 2.0Ghz Pentium 4 also available)

512Mbytes soldered on-board DDR memory expandable to 1.5Gbytes using SODIMM socket

SODIMM socket

**ECM401**

Over 15 years in business of designing and manufacturing embedded computer products for OEMs and System Integrators

#### Features:

- (6) Serial ports

- (4) USB 2.0 ports

- (1) 10/100Base-T • Compact Flash Socket

- E-IDE supports 2 devices

- · Video I/F (1600X1200, 32 Mb)

- AC'97 2.2 Audio

- Less than 5 seconds boot up

- Intelligent thermal management with independent microcontroller

- Power requirement: ■12V @ 3A (2.0Ghz P4, 256MB)

- · Over 200,000 hours MTBF

CPU Fan O System Fan O USB 2.0 3-4 USB 2.0 1-2 USB 2.0 USB 2.0 1-2 USB 2.0 USB 2.0

Power 12V

\_\_\_\_

Keyboard, Mouse, Video, LAN, Speaker

Compact Flash Primary EIDE On/Off Switch

#### We can design your Embedded Computer Board in 30 days.

Time-to-market is very critical to a company's success.

TME has a proven development and manufacturing process that allows new embedded computer products, using TME's core technologies, to be developed in 30 days.

OEMs and System Integrators can now bring their products to the market without compromising cost and features at the expense of time.

#### **Typical Applications**

- Robotic

- Medical

- Avionics

- e-Kiosks

- ▲ Transportation

- ▲ Military/Aerospace

- ▲ Industrial Automation

- ▲ Inventory management

- Point Of Sale Terminal

- ▲ Test & Measurement

ECM401 Embedded Computer Module provides all functions and features of a high performance computer on a very small Module.

Embedded Computer Designers can easily design an I/O board with proper connectors and form factor that is most suitable for their applications.

The ECM401 supports up to 1.5Gbytes DDR memory, 2.8GHz CPU, with built-in Audio, Video, USB, Network, serial, LPT interfaces and PCI BUS extension capability.

#### Toronto MicroElectronics Inc.

5149 Bradco Boulevard, Mississauga, ON., Canada L4W 2A6 Tel: (905) 625 - 3203 - Fax: (905) 625 - 3717 sales@tme-inc.com - www.tme-inc.com

# Hermann Strass

## Technology Passport

### Electronic firefighting

#### Fireproof data center

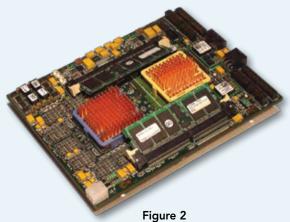

A modern fire engine carries more than just a pump, ladders, and fire hoses. It also contains a distributed multiprocessor data center. The Z8 Airport Crash Tender from Albert Ziegler GmbH, which has manufactured firefighting equipment since 1890, is used at commercial and military airports in Stuttgart (as shown in Figure 1), Zurich, and other places around world.

The fire engine is based on an 8 x 8 chassis with a V12 diesel engine delivering 1,000 metric horsepower. The Z8 weighs 40 metric tons and can rush to the site of a fire at almost 140 km/h. Two tanks carry 15,000 liters of foam and water. A separate pump motor can propel water or a water-foam mixture more than 90 m from the hose nozzle. The fire engine has nozzles all around its body for spraying water and foam to defend itself against approaching fire.

Two Multiprocessor Control Panels (MCP6) with CAN bus networking control the extinguishing unit. The MCP6 units from Graf-Syteco GmbH are located in the fire engine, one inside the driver's cabin (see Figure 2) and one at the rear of the fire engine. Each unit is equipped with an AMD processor, 16 programmable push buttons, two digital potentiometers with push-button functions, four video input channels, two USB 2.0 ports, two CAN ports, eight digital inputs, 10/100 Ethernet, two Pulse Width Modulated (PWM) outputs, several counters, and a TFT display.

The fire engine also has three keyboards with programmable buttons and LEDs in various locations. All electronic items are protected against environmental influences (Enclosure Codes IP65-IP68), including night-vision design and displays that are easily readable in poor visibility environments. The fire engine includes 10 multichip modules that include various digital and analog I/O channels, including PWM variants connected via CAN interfaces.

#### **European events and awards**

The embeddedworld2008 exhibition and conference in Nürnberg (February 26-28) is the world's largest gathering of embedded computing experts. The exhibition set new records for all key figures: 675 exhibitors (+14 percent), 17,341 trade visitors from all over the world (+27 percent) with 56 percent more international attendance, and 18 percent more space, thanks to a new hall.

CEOs and CTOs from Green Hills Software, Infineon, and Kontron provided high-level information related to embeddedworld's three focal points: hardware, software, and tools.

Organizers presented the embedded AWARDs 2008 the day before the

2008 the day before the exhibition. F&S Elektronik Systeme, Germany, received the software AWARD for the Failsafe Flash File System, which continues operating even in the event of a power outage during software updating. Atmel, France, received the hardware AWARD for the first 32-bit microprocessor core with single-cycle SRAM read/write and direct interface to the three-stage pipeline; it does not need a system bus. Hitex, Germany, received the tools AWARD for the STM32-PerformanceStick. The USB stick with peripheral connector and tools software can look deep inside applications, not just the processor core.

Volker Wunsch of the University of Mannheim, Germany, received the university AWARD for a small, self-contained, MEMS-based 6D navigation system for location-based services.

### SYSTEMS THAT CAN GO ANYWHERE, DO ANYTHING.

Extreme cold. Intense heat. Moisture. Vibration. Impact. Dust. Dirt. Grime. No matter what the operating conditions, we pride ourselves on our ability to build high-quality, ruggedized solutions that virtually do whatever it is you want them to, regardless of the conditions you need them to do it under. It's all just part of our dedication to producing the best-in-class computing platforms and displays available on the market. And it's why you need to call us. Because we're not just building durable solutions. We're building a reputation.

UNIQUE COMPUTERS & LCDS

## Expanding multicore, RapidlO, and mobile platform innovation

#### Multicore Association www.multicore-association.org

The Multicore Association provides a neutral forum for vendors interested in, working with, and/or proliferating multicore-related products, including processors, infrastructure, devices, software, and applications. The organization currently has three working groups: Multicore Communications API (MCAPI), Hypervisors, and Multicore Resource Management.

On April 1, the Multicore Association announced that version 1.0 of the MCAPI specification was finished and would soon be available to the public. MCAPI captures the basic elements of intercore communications and scales to support hundreds of processor cores. This API's principal use will be in embedded multicore systems with tight memory constraints and task execution times.

"MCAPI ... has been developed by a wide variety of member companies that range from processor vendors such as Freescale, Intel, MIPS Technologies, and Tilera to software and development tool suppliers such as Codeplay, eSOL, Imperas, PolyCore Software, and Wind River," remarks Multicore Association president Markus Levy. "Such a variety of contributors helps ensure that the specification will be applicable to many different types of multicore systems."

#### **RapidIO Trade Association**

www.rapidio.org

The RapidIO Trade Association enables, supports, and drives development of the RapidIO embedded interconnect and its supporting ecosystem. The group will hold the first of its RapidIO Global Design Summits 2008, "Converge, Learn, Innovate, and Design," on May 21 at the Novotel following WiMAX World EMEA in Munich, Germany. This event will showcase technology experts representing CommAgility, Fabric Embedded Tools, IDT, VMETRO, Mercury Computers, RIOLAB, Texas Instruments, Freescale, Tundra Semiconductor, and Xilinx.

"RapidIO technology is the most efficient multihost/processor available and delivers the lowest cost per bit in the industry," asserts RapidIO Trade Association executive director Tom Cox. "These design summits provide a place for the world's best

designers to converge, learn the latest about the RapidIO specification and its expansive ecosystem, and discover innovative ways to speed high-performance, highly reliable solutions to market."

RapidIO Global Design Summits 2008 attendees will gain practical information on the RapidIO standard, including the latest RapidIO roadmaps and technology updates as well as news from the RapidIO ecosystem.

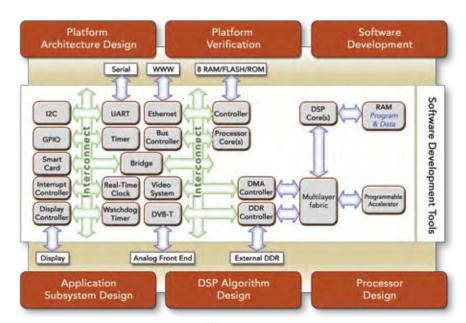

#### Open Handset Alliance www.openhandsetalliance.com

A multinational alliance of technology and mobile industry leaders, the Open Handset Alliance is committed to fostering mobile device innovation and bringing consumers new mobile experiences. The organization's first product, Android, is a truly open and comprehensive platform for mobile devices. Using Android, developers, wireless operators, and handset manufacturers will be able to bring new products to market faster and at much lower cost, giving consumers flexible and more personal mobile experiences.

Built from the ground up, Android allows developers to create novel mobile applications that take advantage of Internet-capable handsets. The mobile platform is built on the Linux 2.6 kernel, offering a robust operating system, comprehensive set of libraries, rich multimedia user interface, and complete set of phone applications. Android's inven-

tive application model makes it easy for developers to extend, replace, and reuse existing software components to produce rich and integrated mobile services.

Developers can download the Android Software Development Kit to create applications for what promises to be an interesting handset platform.

## The Flash Storage Leader

**PQI** Corporation

Tel: (510) 651-7281 Fax: (510) 651-7240

www.pqimemory.com

## Parallel programming for multicore processing

**roblen**

Developers cannot always take advantage of multicore processors without understanding the impact on existing code. Various system architecture combinations make optimization challenging, and keeping code portable can be difficult in heterogeneous designs.

olution

By implementing a code partitioning system, programmers can write complex software scalable for use on parallel processors. Separating data allows multiple memory spaces to improve multicore software performance by allocating memory space for each processor.

#### Filtering out software side effects

Placing multiple processor cores on a single die can improve system performance while reducing power consumption. Embedded designs can benefit from multicore because designers can spread out an embedded device's functions to different cores so that processing units can perform separate tasks concurrently.

Developers want the ability to take a single-core C++ program, pass it through an autoparallelizing compiler, and automatically generate a multicore program. However, single-core C++ software contains many dependencies in which one part of the software must be executed after another part. It is impossible for the compiler to automatically change the program's order of execution to execute several parts of the program at the same time on different processors.

Codeplay's Sieve C++ parallel programming system aims to minimize the amount of programmer intervention required when writing software for multicore processors. Using a *sieve marker*, programmers mark a section of the program called a *sieve block*. Inside sieve blocks, side effects are delayed, meaning that program

Quick facts Codeplay

Founded: 1999

Management: Andrew Richards, founder

and managing director

Headquarters: Edinburgh, Scotland

URL: www.codeplay.com

code inside sieve blocks can be automatically split into three parts: reading data from memory, pure computation, and writing data back to memory. Because of this division, memory operations can be separated, parallelized, and performed by a DMA system. The system is aptly named "Sieve" because it filters out side effects from software and then lets programmers apply them later. Sieve has been tested successfully on the Cell BE-based PlayStation 3 and AGEIA's PhysX processor.

While Sieve represents a step forward, more innovation is needed to make multicore architectures easier to use. The software community must continue to develop better tools and processes that make multicore architectures more practical.

## The right manufacturing partner makes all the difference.

AMAX offers comprehensive prototype development, custom manufacturing, and logistics services that deliver robust quality and performance, rapid time to market, and reliable support for your products.

From custom chassis, bezels, and faceplates to your uniquely branded labels and packaging, AMAX provides quality products with a look and feel that reflects your company identity. With AMAX's global logistics and support services, you can deploy your system anywhere in the world with the necessary support to make your product a success.

Contact us (510) 651-8886 / ext. 8800 or visit us: www.amax.com.

Excessive heat is a significant concern in any computer design. Though designers have implemented varying methods of heat dissipation, all share one common problem. Heat dissipation relies on the transferring medium's thermal conductivity. Many ingenious contraptions have been invented to achieve faster and more efficient heat dissipation. But instead of throwing heat away, why not recycle it? John presents a potentially energy-salvaging thermal management strategy.

Ask most laptop or notebook computer users about their main annoyance, and their responses will likely have something to do with the heat their computers produce. Laptop and notebook computers use many of the same components as embedded computer designs – components such as the central and graphics processing units, Northbridges, Southbridges, and so on.

Components play a significant role in a thermally friendly computer design. Using such low-heat processors like the VIA C7 CPU help reduce overall heat[1]. But generally, as processors become more powerful, they generate more heat, making thermal management an important consideration.

Herein lies the problem: Computers require power to operate, and that power inevitably produces waste energy in the form of heat. If the accumulated heat within a system becomes too great, the system cannot operate properly. Designers' objective, then, is to get rid of the generated heat and use it productively, if possible.

#### Current thermal management techniques

At present, most if not all thermal management methods concentrate on heat dissipation, either passive (for example, fanless heat sinks) or active (for example, fan-forced cooling or water cooling). An ideal thermal management system based on heat dissipation would dissipate all the generated heat. Though existing thermal management devices are adequate, they are limited in how much heat they can dissipate. Heat dissipation is only satisfactory until thermal equilibrium is reached.

How much heat needs to be dissipated? Generally, the amount of energy used is proportional to the amount of heat produced. So if a component uses 30 W of power over 60 seconds, it will output 1,800 joules of heat.

$$Q = Pt = VIt$$

In the equation above, Q represents heat in joules (J), P represents power in watts (W), t represents time in seconds (s), V represents voltage (V), and

I represents current in amps (A). The delta T degree Celsius can be calculated using the following equation, where m represents mass in kilograms (kg) and c represents specific heat (J/gK).

$$\Delta T = Q/mc = VIt/mc$$

A heat-sink system is based on transferring heat from the heat sink to ambient air. For a heat sink to properly work, thermal equilibrium must never be reached while the system is running (that is, ambient air must always be cooler than the heat sink when the system is on). Otherwise, once thermal equilibrium is reached, the heat will no longer transfer from the heat sink to ambient air.

Once thermal equilibrium is reached, the heat sink cannot do much to relieve the processor of its heat burdens. Even assuming that thermal equilibrium is never reached, it is evident that much energy is wasted. Such potential should not go unused. An alternative thermal management technique involves converting heat energy and storing it for later use.

## **CORE SYSTEMS**

Reliable operation in severe environments

- Integrates hardware mechanically, electrically and thermally

- Fanless, total thermal solution

- Mini PCI & PC/104 expansion

- MIL-810F, EN50155 available

- Installed Windows® XPe or Linux available

- Virtually indestructible mobile power supply

- NEMA 4X

- -40° to 85° C

Transportation

- Mining vehicles

- Outdoor kiosks

- Industrial servers

- Digital signage

- Military and police

- Traffic management

- Digital video surveillance

- Asset management

303-430-1500

OCTAGON

www.octagonsystems.com

#### Special Feature: Designing for energy efficiency

#### Making heat productive

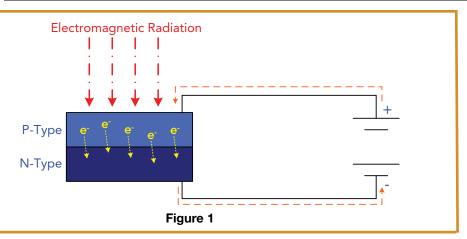

Converting heat energy to electricity is not a new idea. Because heat is infrared radiation and thus part of the electromagnetic spectrum, photovoltaic-based thermal management is possible[2]. The term thermophotovoltaic (TPV) has been used to describe photovoltaic devices for converting heat energy[3]. Currently, TPV devices are not practical enough to consider as primary power sources. However, it is important to remember that thermal management systems' chief objective is heat removal, not power generation. Any power that is gleaned from the process is a bonus and not the main goal.

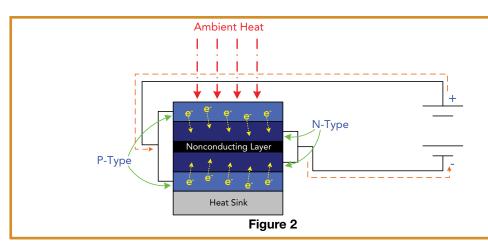

Photovoltaic devices require two layers of photosensitive material: one p-type layer and one n-type layer. The p-type comprises a material whose atoms have an extra electron that prevents the material from being completely nonconductive. The n-type consists of a material whose atoms lack one electron. When the p-type layer is exposed to light, the photons in the light source cause the extra electrons to be released, resulting in a flow of electricity (see Figure 1).

#### Implementation for a fully enclosed system

A thermal management device that recycles waste energy is ideal for airtight sealed systems. In such systems, passive cooling and fan-forced cooling have little if any effect. When waste energy is recyclable, rugged airtight systems can be designed without sacrificing performance. High-performance components generally produce more heat, but for a thermal management device fueled by heat, it is no longer a problem.

To implement the thermal management device, the chassis interior must be lined with TPV cells to absorb as much heat as possible. In addition, a double-sided TPV cell should be placed directly over the heat sink (see Figure 2). Having a double-sided design enables the TPV cell to draw heat not only from the heat sink but also from ambient air. The chassis interior wall is lined with single-sided TPV cells to capture any remaining ambient heat.

This thermal management strategy is particularly suitable for portable applications or external applications where the environment may adversely affect the computer (for example, a street kiosk, GPS unit on a motorcycle, or navigation unit on marine craft). The technique also would work in partially enclosed systems such as fixed applications where the environment will not have adverse effects on the computer (for example, a kiosk inside a building).

#### Perpetuating battery life

By using TPV cells in thermal management devices and choosing the right components, designers can create winning low-heat systems. As photovoltaic cell technology advances, such designs may result in products with ridiculously long battery lives – and perhaps even a nearly perpetual energy source. **FCD**

#### References

- [1] "VIA C7-M ULV Processor," VIA Technologies website. 2007. VIA Technologies, Inc. 6 Dec, 2007. www.via. com.tw/en/products/processors/c7-m\_ulv/ index.jsp

- [2] "Solar Cells that Harness Infrared Light," Environmental Science & Technology. 2 Mar. 2005. Konarka Technologies, Inc. 14 Nov. 2007 www.konarka.com/news\_and\_events/konarka\_articles/2005/3\_march/environmental\_sci\_and\_tech/solar\_cells\_that\_harness\_mar2.php

- [3] "Thermo-photo-voltaic Cell Based on GaSb," TPV Network. 2007. 12 Nov. 2007 tpvcell.hmg.inpg.fr/WT.html

John Lin is a senior technical writer at VIA Technologies, Inc., based in Taipei, Taiwan. He has seven years of experience in the

computer industry, with five-plus years at VIA. John graduated with a Bachelor's degree in Business Economics from UCSB.

VIA Technologies, Inc. +886-2-2218-5452 JohnLin@via.com.tw www.via.com.tw

Switching strategies for increasing processor power efficiency

By Brian Law and Greg Ferrell

Continual advancements in smaller silicon geometries have enabled lower operating voltages in embedded devices, particularly microprocessors. Operating voltages for processor cores are now as low as 1.2 V and quickly moving to 0.8 V, presenting a challenge as to how designers can efficiently power these devices. As opposed to the traditional method of using linear regulators to power low-voltage devices, using switching regulators in these applications can help solve this problem. Depending on system requirements, designers can use various architectures to maximize switching regulators' efficiency.

A typical low-power embedded processor draws 300-600 mA. Using a switching regulator in older-generation processors where core voltages were 3.3 V provided little benefit. However, decreasing core voltages are presenting a significant opportunity for efficiency improvements, especially when powered by a lithium ion cell (4.2 V) or 5 V rail. For example, a linear regulator in a 4.2 V system will waste 1.8 W [(4.2-1.2 V) x 600 mA] when regulating down to 1.2 V. In contrast, a switching regulator can perform with up to 95 percent efficiency under the same conditions, which can add a significant amount of operation time to the system.

The potential noise created by a switching regulator, its inefficiency at light loads, and the need for more complex control have traditionally discouraged designers from using this type of regulator for an embedded processor. Additionally, linear regulators' larger footprint has made linear regulation the preferred method. Nonetheless, designers can employ several techniques that greatly improve efficiency in switching power supplies and make switching regulators feasible in different types of designs. Single ICs

with an integrated controller, pass devices, and compensation components have made switching regulators less design-intensive and more cost-effective to implement.

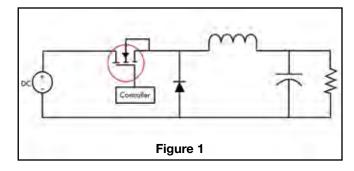

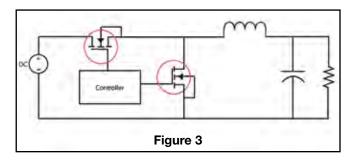

#### Standard buck topology

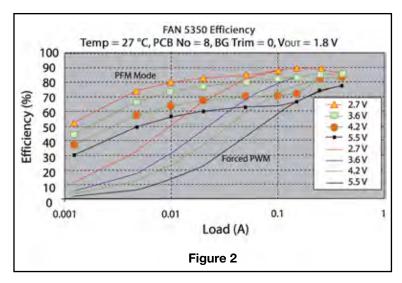

A simple buck switcher comprises a Field-Effect Transistor (FET), diode, inductor, capacitor, and controller, as shown in Figure 1. Regulating output voltage in this topology involves varying the duty cycle on the FET's gate to increase or decrease current through the inductor, a method referred to as *Pulse Width Modulation* (PWM). A PWM switching regulator's efficiency can be upwards of 95 percent when operated at full load. However, when operated at light load, a switching regulator's efficiency drops off significantly, making it undesirable for systems that operate under changing load conditions or require low current or sleep modes.

To overcome a switching regulator's inefficiency during light load conditions, designers can put the regulator in pulse skipping or *Pulse Frequency Modulation* (PFM) mode. When in PFM mode, the FET in the switching regulator only operates when output voltage falls below the low limit. This reduces the number of pulses, which in turn reduces switching losses through the FET, inductor, and diode, thus improving efficiency under light load conditions.

### Reinventing Storage

Rugged, Reliable, Unparalleled

## SATA / IDE SSD

**Solid State Drive**

#### **SATA/IDE SSD**

#### Performance

Operating Temp: -40 to +85C

Sequential Read Rate: 60 MB/sec (min) Sequential Write Rate: 45 MB/sec (min) Sequential Read IOPS: 58,675 IOPS

Access Time: 0.1ms

Power Consumption: 85% less than Average HD

#### Reliability

Shock: 1500G (operating) Vibration: 16G (operating)

MTBF: > 1,000,000

#### Endurance

Read: Unlimited

Write: >140 years @ 50GB write-erase/day

#### "AWARD WINNING PRODUCT"

**Best of Show Award**

- 100% compatible with standard hard disk drives

- IDE form factors in 1.3" / 1.8" / 2.5"

- Designed and manufactured in USA

- Capacities range from 4GB to 256GB

- SATA form factors in 1.8" / 2.5" / 3.5"

#### Special Feature: Designing for energy efficiency

For the device shown in Figure 2, the regulator transitions from PFM to PWM at about 100 mA, thereby maximizing efficiency throughout the entire range of output currents.

When designing with a PFM regulator, designers must take into account the applications in which it will be used. Since the switcher's frequency varies with the output load, it is possible that switching frequency can fall as low as the audio band, which can produce undesirable noise problems. Fortunately, certain tools available in the market today can ensure that frequency never enters the audio band. Although these tools may cause a slight decrease in efficiency under light loads, they can save designers countless hours spent eliminating a noise issue.

#### Synchronous topology

Designers can make additional improvements to a switcher's efficiency using a synchronous topology, as shown in Figure 3. This topology can reduce switching losses and reverse recovery losses through the diode by replacing the diode with a low  $R_{\rm dsom}$  FET.

In this topology, the timing of synchronous switching is critical. If both FETs are conducting, power will be lost on every cycle and efficiency will be compromised. In addition, designers must consider which devices to choose. For example, the FET's gate capacitance is an important variable because it can keep the low side FET in conduction after the controller has switched off the FET. During the short period of time that the gate remains charged, the input power is shunted directly to ground. The R<sub>ds(on)</sub> and FETs' gate capacitance will have the greatest impact on efficiency in this topology; thus, it is important to optimize both.

In the aforementioned topologies, using higher switching frequencies can be advantageous when board space is very limited. Higher switching frequencies allow designers to use smaller passive components such as the inductor and output capacitor, which can decrease the design's cost and overall footprint. However, this comes at the price of decreased efficiency. When frequency increases, the number of times that FETs switch increases, which in turn increases losses. In addition, the smaller inductor and capacitor will likely create higher ripple on output voltage.

#### **Multiphase topology**

To overcome today's stringent ripple requirements while maintaining efficiency in embedded designs, designers can use multiphase DC-DC switchers. This topology can reduce switching losses while effectively increasing the regulator's switching frequency.

For example, consider a single-phase DC-DC synchronous switcher connected to a load,  $I_{load}$ . Switching losses through each FET are  $I^2R$  or  $I_{load}^{2*}R_{ds(on)}$ . In a multiphase design, switching losses are the same through each FET. However, the current in each phase is divided by the number of phases. Therefore, switching losses in a two-phase design can be reduced by:

$$\left(\frac{I_{load}}{2}\right)^2 * R_{ds(on)}$$

or, in general:

$$\left(\frac{I_{load}}{N}\right)^2 * R_{ds(on)}$$

where N is the number of phases in the design.

Additionally, a multiphase design improves the regulator's ripple currents and transient response time. This comes at an increase in cost and footprint because an inductor and two FETs must be added for each phase and because the controller becomes larger and more complex.

#### Narrowing the options

Power efficiency is the key to meeting the demand for extended battery life in portable products. Processor manufacturers have aided this effort by reducing operating voltages, but power supplies must adapt to maximize efficiency. When deciding on the most efficient power supply, it is important to examine the variables to assure the power supply will meet processor requirements. Power supply cost must be part of the decision as well.

The standard buck switcher provides efficiency when operating in a PWM mode and is less complex than the synchronous buck, making it a less expensive option. However, the diode creates a voltage drop, which wastes some power. The synchronous buck reduces this voltage drop using a FET in place of the diode, which increases efficiency but at higher cost.

The multimode regulator provides efficiency improvements over the full load range by switching from PWM to PFM when the processor is in sleep mode. This adds some output ripple voltage, but as long as it stays within the processor's power specification, it will significantly improve battery life. The multiphase regulator maintains efficiency while eliminating much of the output ripple voltage, also at higher cost.

Designers can follow these guidelines when designing power supplies for an embedded processor. All designs require trade-offs, and power supplies are no exception. Given the budget constraints, power requirements, and efficiency target for any design, these strategies will help narrow the options to identify a power supply that provides the best compromise of all three.

Brian Law is a field applications engineer at Fairchild Semiconductor, based in San Jose, California. Prior to Fairchild, he worked as an account

executive for ON Semiconductor and a district manager for Toko. He holds a BS in Electrical Engineering from Iowa State University and is working toward an MBA from the University of Phoenix.

Greg Ferrell is a field applications engineer at Fairchild Semiconductor. Greg has 17 years of experience in engineering design

and field applications engineering, with specific focus on design, test, and field applications for the cellular handset market. He holds a BSEE from Ohio State University and an MSEE from the Illinois Institute of Technology.

Fairchild Semiconductor 207-775-8100

Brian.Law@fairchildsemi.com Greg.Ferrell@fairchildsemi.com www.fairchildsemi.com

## For Harsh Environments -40°C to 85°C Operating Temperature

Five Year Product Availability

#### EMBEDDED COMPUTER

Fanless Dust Tight High Performance Embedded Computer for Outdoor, POS, In-Vehicle, Marine or Applications.

- Pentium M / Pentium 4 / Celeron CPU from 1.3GHz to 2.1GHz

- Over 200,000 hours MTBF

#### DIGITAL VIDEO RECORDER

In-Vehicle Fanless Rugged Digital Video Recorder

- Up to 8 Video and Audio Channels @ 704x480 resolution (D1), 30fps per channel

- Operated from 7V ~ 28V DC-IN

- . +12V DC Out for cameras

- · Anti-vibration and anti-shock mounting kit

#### POINT OF SALE SBC

**Ultra low power** Embedded Computer designed for POS terminals

#### SYSTEM ON MODULE (SOM)

Design your own or have TME design a custom I/O board to be used with TME's SOM

- From 800MHz to 3.4Ghz CPU

- Small form factor 5.5" X 4"

- Up to 1.5 GBytes soldered on-board DDR memory

- ISA, PCI, PCI-Express expansion

#### **EBX FORM FACTOR SBC**

Pentium III 1.2GHz EBX SBC designed for **Mobile** and **Outdoor Applications**.

- Ultra low power, Passive Heat Sink for CPU up to 900 MHz, soldered on-board 256MB SDRAM

- CRT/LCD, Audio, LAN, 6 serial, 4 USB 1.1,

Intelligent thermal management, PC104+ expansion

#### PC/104-PLUS SBC

High Performance PC/104-Plus Embedded Computer (1.2GHz Pentium III)

- · Fanless up to 900MHz

- CRT/LCD, LAN, PCI on PC104+, ISA on PC104 connectors, 2 serial ports, dual USB, 256 Bytes EEPROM, 64-bit unique electronic ID

Toronto MicroElectronics Inc.

5149 Bradco Boulevard, Mississauga, ON., Canada L4W 2A6 Tel: (905) 625 - 3203 - Fax: (905) 625 - 3717

sales@tme-inc.com - www.une-inc.com

## Thermal simulation optimizes cooling in high performance systems

By Kevin Rhoades

Thermal issues present some of the most critical challenges embedded designers face as they try to achieve maximum performance while keeping size, weight, and cost down. Applications in medical, industrial, telecommunications, and military

As operating frequencies increase and process geometries continue to shrink, highperformance processors are becoming the biggest culprit of heat generation, giving off as much as 120 W per processor. With power levels rising, designers need effective tools to

environments have huge performance demands, thereby requiring faster processors.

validate thermal management early in the design process.

#### Importance of thermal design

The lifespan of a component as well as the entire system is directly tied to the heat it generates and the system's internal temperature. Excessive temperatures can result in performance loss and, ultimately, component failures. For embedded systems that require high availability and longevity, this can be disastrous. Consequently, cooling has become an important design consideration. Where designers choose to place components, airflow vents, pressurization, and heat sinks has a measurable effect on thermal management.

To further complicate today's embedded system designs, certain applications have additional requirements for sealed enclosure designs. For example, military equipment must be able to operate in extreme temperature fluctuations and high altitudes where air is thin and ineffective for cooling – all while undergoing extreme vibration and shock. This often

calls for sealed designs that rarely or never exchange enclosure air with outside air, limiting which thermal management techniques designers can employ. These types of rugged designs are often encased with outside protection using high-density rubber that retains heat. Engineers must be mindful of application requirements when determining how to dissipate heat in these designs, particularly rugged handheld computers that cannot be too hot to handle in the field.

#### Thermal management techniques

Embedded system engineers have many options available for addressing heat issues. Heat sinks come in a vast assortment of types and sizes. Several special epoxies allow a heat sink to be glued to a component, providing increased surface area to dissipate heat away from the IC. Mechanically modifying the embedded system enclosure and mounting custom-designed heat sinks can remove heat from

individual or multiple components. The back corners of the chassis can act as heat traps, allowing special baffles to deflect air to a particular location.

Internal component-mounted as well as enclosure-mounted fans can be incorporated to provide a constant airflow directly to the components and the internal system circuit board. When system design restrictions prohibit using fans or advanced cooling systems and require hermetically sealed enclosures, designers must often resort to more creative methods. Utilizing a different board with decreased features, reduced clock speeds or an alternate CPU, and more power-efficient storage is sometimes the only way to resolve thermal problems in these designs.

However, predicting and adjusting a system's thermal footprint is only part science. Thermal management requires

ndustrial equipment needs to perform flawlessly, night and day, under even the most extreme conditions. Whether designing for the manufacturing floor, clean room or the field, you can depend on VersaLogic to deliver the highest quality embedded computer products, from prototyping and design-in, through years of product production. We design our boards for high reliability and long-term availability, then run them through exhaustive quality tests, ensuring that we deliver only the best. And with our world class service and five year availability guarantee, we'll always be there when you need us. Whether you need one of our standard products or a customized version, our skilled technical staff

will work to meet your exact requirements.

Contact us to find out how for more than 30 years we've been perfecting the fine art of extra-ordinary support and on-time delivery: One customer at a time.

some guesswork or tribal knowledge based on an engineer's previous experience. Yet there is no guarantee that the engineer will pick the right combination of values to investigate which one will lead down a time-consuming path of trialand-error refinement techniques.

#### New technologies eliminate guesswork

To help improve the design's overall reliability and avoid costly redesigns, thermal management must be validated early in the design process so that any problems can be addressed before the hardware is built. New technologies like Computational Fluid Dynamics (CFD) software are making it possible for engineers to effectively deliver thermal management expertise early in the design process long before physical prototyping and testing.

Prior to CFD software, an engineer would attack thermal issues through a cycle of exercises. Each approach required building a prototype, then taking the thermal measurements and making modifications until the desired thermal results were achieved. This often took months of building and testing before the correct design was identified, increasing time to market.

Today, simulation tools can enable engineers to create virtual models of electronic equipment, perform thermal analysis, and test design modifications quickly (often in less than 24 hours) and easily in the early stages of the design process. With a few mouse clicks, designers can rapidly develop "what-if" models, calculate the results, and compare performances.

Flomerics' FLOTHERM software is an example of an application designed to address the challenges of modeling thermal management in electronic and electrical systems. The software enables users to predict airflow and heat transfer in and around electronic equipment, including the coupled effects of conduction, convection, and radiation.

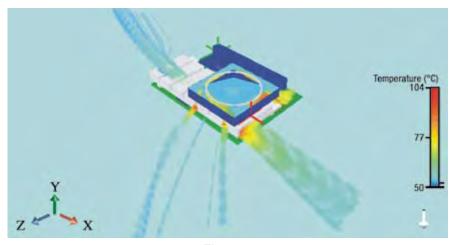

Figure 1 illustrates the active heat-sink temperature plot of an ETXexpress module using this software. The stream in blue to red flowing through the heat-sink fins represents the airflow blowing from

Figure 1

Figure 2

the fan on top. The right side shows the temperature reading starting at +50 °C from blue to red.

Thermal simulation can be helpful in designing an optimal chassis cooling system. The ability to create a model environment that predicts airflow, temperature, and heat transfer and validates the thermal design can cut design time significantly. An independent survey by the Aberdeen Group found that thermal analysis software users completed thermal design verification 3x faster and had

more than 40 percent fewer re-spins on average per PCB design than nonusers.

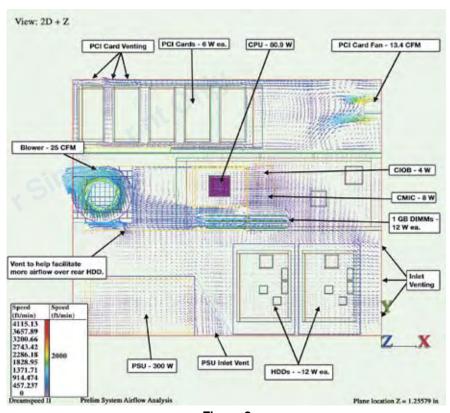

#### Thermal analysis in action

Figure 2 illustrates the preliminary system airflow analysis showing airflow direction, magnitude of speed, and fluid field strength on a 1U chassis temperature vector plot. Using this analysis, engineers can determine if individual commodities on the board need to be moved or replaced or if a particular component or its placement is causing a temperature anomaly.

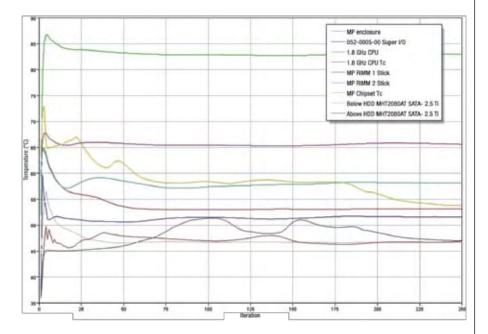

Figure 3

Kontron used FLOTHERM in a network appliance wireless server design because of its ability to reliably simulate the final system's performance and predict worst-case scenarios early in the design process. This particular system had several unknown variables and was based on proprietary cards that were available only as a specification at the time. To complicate matters, the spec had a wide range of power variables from 60-120 W.

Kontron's engineering team took the specification and assigned different values to the CPU, HDD, memory, and I/O to generate a number of scenarios. Figure 3 shows an example of a small form factor monitor point graph that illustrates the temperature of different variables, such as the enclosure, CPU, and other components within the chassis. This simulation provided designers a view into the chassis to see thermal characteristics and anomalies and allowed them to predict worst-case scenarios, including what would happen in the event of a fan or other key component failure.

Once designers validated the model using simulation tools, they built a prototype and tested it in the customer's real-world environment. Because analysis was completed early on and the results were virtually validated using simulation tools, the design held up to the customer's needs.

#### Tools ensure reliability

Thermal requirements must be addressed at the beginning of the design cycle in today's high-performance embedded systems. With the advent of CFD, engineers can virtually e iminate prototyping time and cost, software can pick the direction in which to move the parameters, and users can find the optimum design. Using this conceptual design process, thermal simulation can provide engineers with a key tool to reduce design time and the number of re-spins. Perhaps even more importantly, making good use of these tools enables designers to predict and plan for failures – reducing design risks and improving reliability for missioncritical applications. **ECD**

Kevin Rhoades is VP of business development at Kontron America, where he is responsible for managing the North American Systems Division in Poway,

California. Kevin has 25 years of experience in global supply chain and contract manufacturing and holds a BS in Business from Gonzaga University in Spokane, Washington.

Kontron America 888-294-4558 sales@us.kontron.com www.kontron.com

Thermal and power management

## Thermal concepts enhance DRAM memory subsystem designs

By Phan Ho<u>ang</u>

Controlling thermal issues related to the CPU is often a top priority for designers; however, the memory module is not necessarily less important. Thermal management presents challenging design considerations within embedded environments, requiring knowledge, precision, and creativity to diagnose and overcome memory subsystem design parameters.

In the past, memory was not as complex and did not warrant the same kind of thermal attention that designers paid the CPU. Because the CPU required cooling, chipsets came equipped with heat sinks as a production standard. By comparison, the memory module needed only minor airflow adjustments to keep temperatures in check. But with DDR3 and DDR4 technology increasing speeds in today's embedded designs, memory module design is complex and requires thermal attention as well.

Clock speed is just one reason why memory is running hotter than ever. The customer environment, overall design choices such as memory modules' location on the board, horizontal or vertical module orientation, and the amount of airflow over the system also can influence memory modules' thermal condition.

Embedded system designers typically work with tight board layouts requiring near-perfect engineering to achieve flawless signal integrity and extreme performance. Though other design issues exist, successful system designers consider memory thermal management as a higher-level design issue, keeping abreast of evolving memory technologies and thermal management techniques for reducing heat in memory modules.

Memory designers can mitigate heat and design better memory subsystems using a range of simple but powerful thermal concepts. Similarly, system designers can enhance products by incorporating those concepts when creating their designs.

#### The heat is on

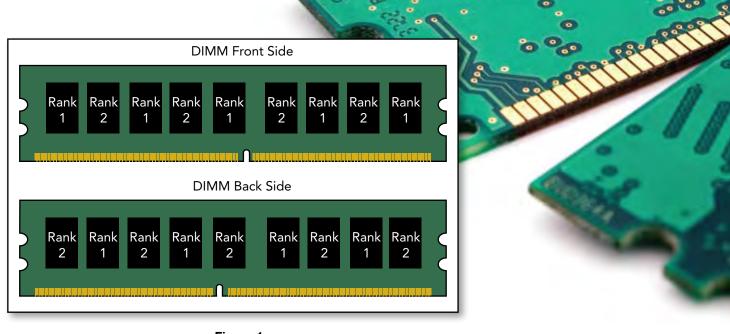

Memory designers begin the process by choosing memory modules that mitigate heat and deliver the best overall heat reduction scheme. Incorporating modules that use the least amount of DRAM within the greatest number of module ranks can achieve the desired module density and manage power effectively. The more DRAM in standby mode, the less power the module consumes – frequently achieved by using DRAM with the widest data bus, as shown in Table 1. For example, a 36-chip four-rank x8 DIMM uses less power than a 36-chip two-rank x4 DIMM.

For an additional example, a 512 MB error-correcting code DIMM can be made using five 64x16 DRAM chips versus nine 64x8 DRAM, resulting in 44 percent heat reduction. The actual reduction may be slightly less due to differences in IDD

|      | ECC (x72) |        |        |

|------|-----------|--------|--------|

| DRAM | 1 rank    | 2 rank | 4 rank |

| x16  | 5         | 10     | 20     |

| х8   | 9         | 18     | 36     |

| х4   | 18        | 36     | 72     |

| nonECC (x64) |        |        |  |  |

|--------------|--------|--------|--|--|

| 1 rank       | 2 rank | 4 rank |  |  |

| 4            | 8      | 16     |  |  |

| 8            | 16     | 32     |  |  |

| 16           | 32     | 64     |  |  |

Table 1

values specified in the datasheets for 64x16 and 64x8 DRAM. Memory designers would typically explore whether or not the memory controller chipset can support the wider DRAM data bus width.

Overall, memory modules appropriately spaced between DRAM either non-stacked or without large, hot semiconductors will have better thermal characteristics. Small form factor memory such as stacked very low profile or stacked SODIMMs have higher power density (watts/area) and need special considerations for cooling. Fully buffered DIMMs also have high power densities because of onboard advanced memory buffer and may require additional cooling aids or airflow.

#### System versus memory

Thermal sensors are critical tools for memory designers. JEDEC's standard specifies that memory modules have thermal sensors to give users monitoring and triggering mechanisms that adjust system performance according to fluctuations in temperature.

Depending on defined parameters, the system can issue an extended mode register set command, which would double the internal refresh rate on the DDR2 DRAM to a 32 millisecond period (tREFI = 3.9 microseconds) at a trigger temperature of +85 °C to extend the DRAM operating temperature to +95 °C. If that feature is not available, designers can incorporate special programming on the memory module for extended temperature operation. Alternatively, the system can use closed loop dynamic temperature throttling and fan speed control to optimize memory performance.

The key point here is that the CPU manages the memory board's thermal sensors, demonstrating that system-level and board-level thermal issues are closely related. The system's BIOS reads output from the sensor and evaluates performance options based on preprogrammed thresholds identifying acceptable temperature ranges. For example, if the memory runs over the limited temperature, the system thermal monitor alerts administrators about temperatures

#### Embedded Computer Solutions For Harsh Environments -40°C to 85°C Operating Temperature

Five year product availability

#### Micro-P3

#### \$US 275.00/each

(OEM Qty. 900Mhz CPU, 256K L2 cache)

- Choice of ultra low power Tualatin Pentium III / Celeron CPU from 500MHz to 1.26GHz with 256/512 3.6 KB L2 cache

- Up to 512MB SDRAM

- Intelligent thermal management with independent microcontroller

- Over 200,000 hours MTBF

- 5V @ 2.2A, 3.3V @ .7A with

900 MHz CPU and 256 MB memory

CRT/LCD video •

Dual channel enhanced IDE • 10/100Base-T •

AC'97 2.2 Audio • 2 RS232 Ports •

1 LPT Port - 2

4 USB 1.1 Ports • 8 GPIO Ports • 2

Keyboard and Mouse • +3.3V •

5831

#### Pentium III EBX SBC designed for Mobile and Outdoor Applications

- 500MHz to 1.26GHz Pentium III CPU

- Ultra low power

- Passive Heat Sink for CPU up to 900MHz

- 14W (using 900Mhz CPU, 256K L2 cache)

- -40°C to +85°C operating temperature

- Soldered Onboard 256MB SDRAM (Optional 768MB with SODIMM)

- CompactFlash Disk (up to 6 Gbytes)

- LCD/CRT Video, 10/100Base-T Ethernet interface, AC'97 Audio, TV Out

- 6 serial ports, dual USB, 256 Bytes EEPROM, 64-bit unique electronic ID

- 128/512Kbytes battery backed SRAM with 10 years data retention

- Intelligent thermal management with independent microcontroller

- . Less than 4 seconds boot up time

- 8" x 5.75" standard EBX form factor

- . Supports DOS, Windows 98, NT, 2000, XP, CE, QNX, pSOS, Linux, VxWorks

#### Toronto MicroElectronics Inc.

5149 Bradco Boulevard, Mississauga, ON., Canada L4W 2A6 Tel: (905) 625 - 3203 -- Fax: (905) 625 - 3717 sales@tme-inc.com -- www.tme-inc.com

#### Hardware: Thermal and power management

above defined thresholds, prompting them to take the necessary steps to lower the temperature, such as checking processors and chassis fans, addressing any chassis airflow vents that may be blocked, or adding another chassis fan.

#### **Airflow matters**

Airflow is a simple but critical issue for memory; the primary goal is to avoid blowing preheated air directly over the memory subsystem. Whenever possible, designers should place the memory subsystem on

Windows\*

www.advantech.com/applied

the sides of the processor and outside the flow of warm air generated by the processor's heat sink or other hot components such as the power supply or chipset. The ambient intake air should flow evenly over the memory subsystem and other hot components such as the processor.

Too small an air gap between modules may create airflow back pressure from the physically obstructed DIMM modules within the airflow path. This could result in an airflow pressure drop along the side

> 38 Tesla, Suite 100 Irvine, CA 92618

Toll Free: 1-800-866-6008

Email: ECGInfo@advantech.com

Phone: 949-789-7178 Fax: 949-789-7179 of the DIMMs, generating a decrease in airflow, or could divert the airflow away or around the entire memory subsystem. DIMM socket spacing should be 10 mm or greater from center to center.

In general, maximizing airflow extracts heat away from the memory. Designers should use a blower or dual fans to optimize airflow if acoustical noise is not an issue. Airflow with a minimum pressure drop is best achieved by extracting the hot air at the exhaust point but also can be improved by pushing air in at the intake point. Plenums, ducts, or shrouds can be used to direct and contain the airflow through the memory subsystem, flowing parallel to the longest sides of the DIMMs and on both sides. These enclosures may allow for slower fan speeds with less acoustical noise and not affect airflow.

Memory modules can be designed to allow airflow across the short side of the DIMM, eliminating heat from being dragged across the long side of the DIMM. This type of mezzanine connector technique does not expose as much DRAM to preheated air from upstream DRAM.

If the motherboard or system board is mounted flat and perpendicular to the line of gravity, the best orientation for the memory would be a vertical mount since hot air rises up along the line of gravity. A vertical DIMM orientation prevents heat from being trapped under the lower bottom side of the memory modules. If a vertical mount is not possible, then an angled-mount DIMM orientation would benefit from one-sided DIMMs with the DRAM components mounted on the top side. This would hold true for memory DIMMs placed flat over the system board as well.

Designers should choose a module with a DRAM placement that does not allow all the DRAM devices to be active on the same side at the same time. Modules with alternating DRAM placements on each side of the memory module per rank will evenly disperse the heat surrounding the DIMM. If airflow is restricted on one side of a DIMM, memory modules with DRAM placed only on the side with the maximum airflow will perform better at

Figure 1

higher temperatures. Figure 1 illustrates how the technique of alternating DRAM ranks can reduce thermal impact.

#### Heat spreaders and more

Heat spreaders are metal covers placed on the surface of a memory module to disperse heat evenly across the surface and equalize surface temperature by removing localized hot spots. A heat spreader is made of a thermoconductive material such as copper or aluminum in the shape of a clamshell wrapped around the memory module.

If space permits, a heat sink placed on the side surfaces of the memory and/or top edge of the memory module will maximize heat extraction from the module. The additional surface area the heat sink adds to the memory module without affecting airflow determines its overall effectiveness.

Heat-conducting PCBs and PCB cores are also effective options. These metal or carbon composite laminated layers are embedded into the structure of the memory PCB to allow it to operate cooler than standard FR-4. The layers also equalize component temperatures by removing localized hot spots like the phase-locked loop. It is not uncommon to see numerous hot spots created via holes under hot devices to conduct heat into the core. These cores in turn conduct heat into the edge fingers of the module and can be brought to the top edge of the PCB to expose it to heat

spreaders or heat sinks. The top edge of this type of PCB has the inner thermal core of the DIMM connected to an integrated heat sink at the top of the module, adding additional height to the DIMM.

During the manufacturing process, memory modules can be tested at elevated temperatures in customers' systems running customers' diagnostic software. This active burn-in will screen out potentially weak modules. Passive burn-in (on unpowered modules) has no effect on screening out DRAM with weak cells because DRAM cells are semiconductorbased capacitors that need to be continually recharged or refreshed to retain binary information. Some memory modules are available using DRAM screened for an extended operating temperature range of -40 °C  $\leq$  Tcase  $\leq$  +95 °C. This is a specialty item, and not all DRAM suppliers offer industrial temperature DRAM as an option for commercial temperature  $(0 \, ^{\circ}\text{C} \leq \text{Tcase} \leq +85 \, ^{\circ}\text{C}).$

#### Thermal matters across the board

Thermal management issues are evolving with memory technology and becoming critical to embedded systems' reliability and performance. The design dynamic between system designers and memory subsystem designers is also evolving and can impact designs built for endurance and performance. Trusted system-level and board-level partnerships plus greater understanding of current thermal concepts

associated with DRAM memory modules can make all the difference in the final product's success.

Understanding DRAM memory module thermal considerations as part of proven system design tenets can equip designers with a new level of understanding regarding ways to improve thermal performance. General design considerations and alternative thermal options can create a winning memory subsystem design, effectively meeting system requirements for the high memory bandwidth, large memory densities, small physical space, and low cost imperative in embedded environments.

Phan Hoang is chief engineer and director of R&D at Virtium Technology in Rancho Santa Margarita, California. Phan began

his career as a design engineer specializing in memory module design and holds a stacked memory package patent. He has Associate and Bachelor degrees in Computer Electrical Engineering, Business, and Management/Marketing from the University of Phoenix.

Virtium Technology 949-888-2444 ext. 141 phan.hoang@virtium.com www.virtium.com

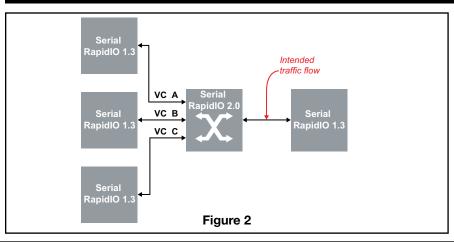

Further enhancing the RapidlO Interconnect Architecture, Serial RapidlO 2.0 offers system designers improved abilities to control, optimize, and accelerate traffic using Virtual Channels (VCs). By implementing techniques explored in this article, future switches can enable VC features even in Serial RapidlO 1.3 systems and facilitate the evolution to Serial RapidlO 2.0 systems.

Serial RapidIO is a high-performance packet-based technology that can be found in an increasing array of applications, including the wireless infrastructure, storage, medical imaging, and military markets. Serial RapidIO's strength lies in its efficient application-driven features and the breadth of its adoption. The switched fabric continues to offer embedded system designers more compelling features with the Serial RapidIO 2.0 specification.

With the Serial RapidIO 2.0 standard, system designers can select link rates from 1.25-6.25 Gbps and port widths from 1-16x, providing high granularity to select a port's data rate best suited to individual applications. Beyond the physical layer enhancements, Serial RapidIO 2.0 offers several higher-level features designed to provide greater control over the switch fabric traffic flow.

VCs grant the ability to control how different types of traffic flow through the system. VCs allow system designers to control packet flow by dividing the link into separate channels and assigning packets to a particular channel. The first VC, VC0, is a backward-compatible VC provided in Serial RapidIO 2.0 that operates like a Serial RapidIO 1.3 compliant link. Beyond this, Serial RapidIO 2.0 supports up to eight more VCs (VC1-VC8).

#### **Controlling traffic**

VCs offer a variety of enhancements to control data flow in the fabric. Each VC can be guaranteed a portion of the link bandwid h System designers have control over how multiple traffic types interact and can, in effect, insulate them from one another through bandwidth allocation. Latency-sensitive traffic, such as streaming video, can be allocated a guaranteed portion of bandwidth throughout the switch fabric. This enables system designers to ensure a high-quality experience for consumers because a minimum level of performance can be guaranteed regardless of other traffic present in the switch fabric.

When a VC demands less than its guaranteed bandwidth, Serial RapidIO 2.0 allows other VCs to use that available bandwidth, thus maximizing link utilization. In essence, bandwidth allocation is intelligent, simultaneously ensuring that a greedy VC demanding more than its allocation cannot rob bandwidth from another VC and that bandwidth does not go unused when packets need to be sent.

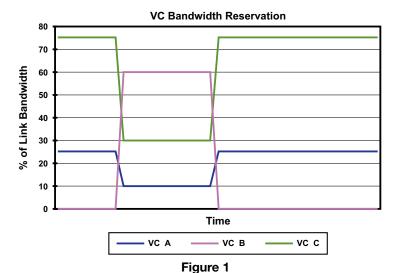

Figure 1 shows the benefits of VC bandwidth reservation. Three packet streams share a link and are allocated bandwidth such that 10 percent is dedicated to VC\_A, 60 percent to VC\_B, and 30 percent to VC C.

In the first part of the simulation, only VC\_A and VC\_C need packets transmitted, so their bandwidths increase beyond their allocations to take advantage of the unused portion allocated to VC\_B. As shown, VC\_C occupies 75 percent of the available link bandwidth while VC\_A uses the remaining 25 percent. Serial RapidIO 2.0 allows VCs with packets present to access the unused part of the link in proportion to their bandwidth allocations.

Later in the simulation, VC\_B needs traffic sent via the shared link. Serial RapidIO 2.0 allows the switch to rapidly respond to the change in traffic and alter bandwidth usage as needed to match the programmed allocations. In this case, the switch quickly gives an intermittent but latency-sensitive stream such as VC\_B its 60 percent allocation. Once the packets from VC\_B are transmitted, the switch reapportions link usage to the remaining VCs with packets awaiting transmission.

#### **Changing channels**

Serial RapidIO 2.0 provides an additional level of control over link partitioning by offering a function unique to VC0. VC0 can be configured to obey bandwidth reservations. Alternatively, it can be configured to automatically obtain any bandwidth it requires while any remaining bandwidth is divided among all other VCs with packets

awaiting transmission. This allows control plane traffic transmitted via VC0 to operate completely independent of data plane traffic and only be constrained by Serial RapidIO 1.3 compliant priority rules.

VCs offer two modes of packet transmission – Continuous Transmission (CT) and Reliable Transmission (RT). RT operates like earlier versions of Serial RapidIO in that retransmitting a packet when it cannot be received makes packet transmission lossless. CT is optimized to achieve low latency for traffic flows that can accommodate packet loss by not performing retransmissions. VC0 supports all defined priorities and operates exclusively in RT mode.

Higher VCs (1-8) can operate in CT or RT mode, allowing customers to optimize the transportation method for different types of data. For example, whereas control plane traffic may require the responses and guaranteed delivery that RT mode provides, data plane traffic (such as from an audio stream) may benefit from CT mode's reduced latency and possibly suffer if retransmissions are performed.

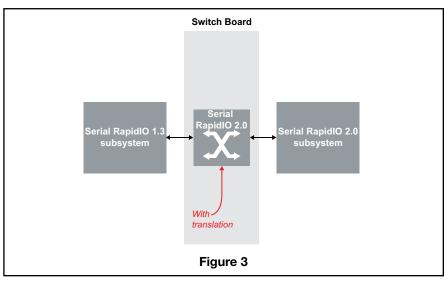

#### Switches take on the challenge

Integrating a specification's new features into present and next-generation systems presents a challenge. Backward compatibility is a cornerstone of the Serial RapidIO specification development process, but promoting progression toward the new standard is equally important. System developers will begin to see more Serial RapidIO 2.0 compliant products in the near future. However, the ecosystem cannot completely transition at once.

Switch vendors will likely be among the first to adopt Serial RapidIO 2.0. Switches serve as the foundation of embedded fabric ecosystems and, in essence, validate new specifications. Processing end points, such as DSPs and FPGAs, may lag in producing new devices compliant to a specification's latest revision. Switch vendors are thus presented wi h a unique challenge to produce next-generation solutions and, at least initially, market them into sys ems limited to current-generation technology based on available end points.

Designers will migrate to end points that support Serial RapidIO 2.0 as existing systems evolve or new ones are initiated. Inevitably, Serial RapidIO 1.3 and Serial RapidIO 2.0 availability will overlap for an extended period of time. Systems that require Serial RapidIO 1.3 subsystems to communicate with Serial RapidIO 2.0 compliant subsystems will likely exist for an even longer period of time.